## Power, Performance, and Upheaval: An Opportunity for Managed Languages

**Ting Cao**

A thesis submitted for the degree of Doctor of Philosophy The Australian National University

Except where otherwise indicated, this thesis is my own original work.

Ting Cao

28 July 2014

## Acknowledgments

There are many people and organizations I wish to acknowledge for their support and encouragement during the course of my PhD.

First I would like to thank my supervisors Prof. Steve Blackburn and Prof. Kathryn McKinley for their guidance and support. They are both very intelligent, inspirational, conscientious, generous, and truly considerate of students. This work would not have been possible without their help.

I would also like to express my gratitude to the Chinese Government and the Australian National University for the financial support. Many thanks to my undergraduate and master supervisor, Prof. Zhiying Wang, for his encouragement and support during my studies in China and my study overseas.

I would like to thank the members of the Computer System Group in the Research School of Computer Science, in particular Dr. Peter Strazdins, Prof. Alistair Rendell and Dr. Eric McCreath for their informative discussions and feedback.

I would also like to express my gratitude to my main student collaborators, Dr. Hadi Esmaeilzadeh, Xi Yang, Tiejun Gao, and Ivan Jibaja. I really enjoyed working with them and I have learnt a lot from them.

I am grateful to the support and help from everyone in our lab, Dr. John Zigman, Dr. Daniel Frampton, Xi Yang, Vivek Kumar, Rifat Shahriyer, Tiejun Gao, Yi Lin, Kunshan Wang, Brian Lee and James Bornholt. I feel very lucky to be able to work with these excellent and friendly fellows. Special thanks to Dr. John Zigman for his long term support of my work and for helping proofread my thesis.

Many thanks to my best friends in Australia, Dr. John Zigman, Tan Vo and Wensheng Liang. They care about me and are always there to provide assistance when I need it. Also, thanks to my friends Leilei Cao, Xinyue Han, Xu Xu, Jing Liu, Jie Liang, and Shi Wang. My life in Australia is much more colourful with their company.

Finally I would like to thank my family, especially my parents and grandparents for their positive role in my education and development. Thanks to my boyfriend Jiaxi Shi, who surprisingly is still my boyfriend after twelve years.

## **Abstract**

Two significant revolutions are underway in computing. (1) On the hardware side, exponentially growing transistor counts in the same area, limited power budget and the breakdown of MOSFET voltage scaling are forcing power to be the first order constraint of computer architecture design. Data center electricity costs are billions of dollars each year in the U.S. alone. To address power constraints and energy cost, industry and academia propose Asymmetric Multicore Processors (AMP) that integrate general-purpose big (fast, high power) cores and small (slow, low power) cores. They promise to improve both single-thread performance and multi-threaded throughput with lower power and energy consumption. (2) On the software side, managed languages, such as Java and C#, and an entirely new software landscape of web applications have emerged. This has revolutionized how software is deployed, is sold, and interacts with hardware, from mobile devices to large servers. Managed languages abstract over hardware using Virtual Machine (VM) services (garbage collection, interpretation, and/or just-in-time compilation) that together impose substantial power and performance overheads. Thus, hardware support for managed software and managed software utilization of available hardware are critical and pervasive problems.

However, hardware and software researchers often examine the changes arising from these on going revolutions in isolation. Architects mostly grapple with microarchitecture design through the narrow software context of native sequential SPEC CPU benchmarks, while language researchers mostly consider microarchitecture in terms of performance alone. This dissertation explores the confluence of the two trends.

My thesis is that there exists a synergy between managed software and AMP architectures that can be automatically exploited to reduce VM overheads and deliver the efficiency promise of AMP architectures while abstracting over hardware complexity.

This thesis identifies a synergy between AMP and managed software, and addresses the challenge of exploiting it through the following three steps. (1) It first systematically measures and analyzes the power, performance, and energy characteristics of managed software compared to native software on current mainstream symmetric hardware, which motivates the next part of the thesis. (2) It next demonstrates that VM services fulfil the AMP workload requirements and tailored small cores for VM services deliver improvements in performance and energy. (3) Finally, it introduces a dynamic scheduling algorithm in the VM that manages parallelism, load balance and core sensitivity for efficiency.

This thesis is the first to quantitatively study measured power and performance

at the chip level across hardware generations using managed and native workloads, revealing previously unobserved hardware and software trends. This thesis proposes solutions to the 40% overhead of VM services by using tailored small cores in AMP architectures. This thesis introduces a new dynamic VM scheduler that offers transparency from AMP heterogeneity and substantial performance and energy improvements.

Those contributions show that the opportunities and challenges of AMP architectures and managed software are complementary. The conjunction provides a winwin opportunity for hardware and software communities now confronted with performance and power challenges in an increasingly complex computing landscape.

## **Contents**

| Ac | knov              | vledgm                           | ents                                                                                                                                                                                                                                                                                       | vii                                                |

|----|-------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Ał | strac             | et                               |                                                                                                                                                                                                                                                                                            | ix                                                 |

| 1  | 1.1<br>1.2<br>1.3 | Scope                            | em Statement                                                                                                                                                                                                                                                                               | 2                                                  |

| 2  | Bacl 2.1 2.2      | Single 2.1.1                     | d and Related Work  -ISA Asymmetric Multicore Processors  AMP Utilization  ged Language Virtual Machines  Garbage Collector  Just-In-Time Compiler  Interpreter  VM Overhead  2.2.4.1 VM Performance Overhead Studies  2.2.4.2 VM Energy Overhead Studies  2.2.4.3 Hardware Support for GC | 6<br>7<br>8<br>9<br>10<br>10<br>10                 |

|    | 2.3               | Summ                             | nary                                                                                                                                                                                                                                                                                       |                                                    |

| 3  | Pow 3.1 3.2       | 3.2.2<br>3.2.3<br>3.2.4<br>3.2.5 | Performance Characteristics for Language and Hardware uction                                                                                                                                                                                                                               | 16<br>16<br>18<br>19<br>20<br>20<br>21<br>21<br>23 |

|    | 3.3               | 3.2.6<br>3.2.7<br>Perspe         | Reference Execution Time, Reference Energy, and Aggregation . Processor Configuration Methodology                                                                                                                                                                                          | 24                                                 |

**xii** Contents

|   |              | 3.3.1                                          | Power is Application Dependent                   | 26 |  |  |  |

|---|--------------|------------------------------------------------|--------------------------------------------------|----|--|--|--|

|   |              | 3.3.2                                          | Historical Overview                              | 28 |  |  |  |

|   |              | 3.3.3                                          | Pareto Analysis at 45 nm                         | 31 |  |  |  |

|   | 3.4          | Featur                                         | re Analysis                                      | 33 |  |  |  |

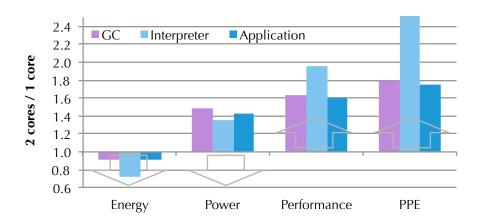

|   |              | 3.4.1                                          | Chip Multiprocessors                             |    |  |  |  |

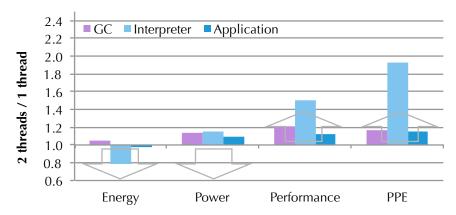

|   |              | 3.4.2                                          | Simultaneous Multithreading                      | 36 |  |  |  |

|   |              | 3.4.3                                          | Clock Scaling                                    | 38 |  |  |  |

|   |              | 3.4.4                                          | Die Shrink                                       |    |  |  |  |

|   |              | 3.4.5                                          | Gross Microarchitecture Change                   | 43 |  |  |  |

|   |              | 3.4.6                                          | Turbo Boost Technology                           |    |  |  |  |

|   | 3.5          | Summ                                           | nary                                             |    |  |  |  |

| 4 | Asv          | mmetri                                         | ic Multicore Processors and Managed Software     | 49 |  |  |  |

| _ | 4.1          |                                                | luction                                          |    |  |  |  |

|   | 4.2          |                                                | odology                                          |    |  |  |  |

|   | 1            | 4.2.1                                          | Hardware                                         |    |  |  |  |

|   |              | 4.2.2                                          | Power and Energy Measurement                     |    |  |  |  |

|   |              | 4.2.3                                          | Hardware Configuration Methodology               |    |  |  |  |

|   |              | 1.2.0                                          | 4.2.3.1 Small Core Evaluation                    |    |  |  |  |

|   |              |                                                | 4.2.3.2 Microarchitectural Characterization      |    |  |  |  |

|   |              | 4.2.4                                          | Workload                                         |    |  |  |  |

|   |              | 4.2.5                                          | Virtual Machine Configuration                    |    |  |  |  |

|   |              | 1.2.0                                          | 4.2.5.1 GC                                       |    |  |  |  |

|   |              |                                                | 4.2.5.2 JIT                                      |    |  |  |  |

|   |              |                                                | 4.2.5.3 Interpreter                              |    |  |  |  |

|   | 4.3          | Motiv                                          | ation: Power and Energy Footprint of VM Services |    |  |  |  |

|   | 4.4          |                                                | ability of VM Services to a Dedicated Core       |    |  |  |  |

|   | 4.5          | Amenability of VM services to a Dedicated Core |                                                  |    |  |  |  |

|   | 1.0          | 4.5.1                                          | Small Core                                       |    |  |  |  |

|   |              | 4.5.2                                          | Microarchitectural Characterization              |    |  |  |  |

|   |              | 1.0.2                                          | 4.5.2.1 Hardware Parallelism                     |    |  |  |  |

|   |              |                                                | 4.5.2.2 Clock Speed                              |    |  |  |  |

|   |              |                                                | 4.5.2.3 Memory Bandwidth                         |    |  |  |  |

|   |              |                                                | 4.5.2.4 Last-level Cache Size                    |    |  |  |  |

|   |              |                                                | 4.5.2.5 Gross Microarchitecture                  |    |  |  |  |

|   |              | 4.5.3                                          | Discussion                                       |    |  |  |  |

|   | 4.6          |                                                | ling Future AMP Processors                       | 69 |  |  |  |

|   | 4.7          |                                                | er Opportunity for the JIT                       | 70 |  |  |  |

|   | 4.8          |                                                | nary                                             | 71 |  |  |  |

| 5 | <b>A 1</b> 7 | M Cab                                          | eduler for AMP                                   | 73 |  |  |  |

| J | 5.1          |                                                | luction                                          | 73 |  |  |  |

|   | 5.2          |                                                | oad Analysis & Characterization                  |    |  |  |  |

|   | 5.2          |                                                | mically Identifying Workload Class               |    |  |  |  |

|   | ٠.٠          | U y 1 lal                                      | IIICAII Y IACIIII YIII Y YYUI NIUAU CIASS        | 70 |  |  |  |

Contents xiii

|   | 5.4 | Speed   | up and Progress Prediction Model 80           |

|---|-----|---------|-----------------------------------------------|

|   | 5.5 | The W   | ASH Scheduling Algorithm                      |

|   |     | 5.5.1   | Overview                                      |

|   |     | 5.5.2   | Single-Threaded and Low Parallelism WASH 84   |

|   |     | 5.5.3   | Scalable Multithreaded WASH                   |

|   |     | 5.5.4   | Non-scalable Multithreaded WASH               |

|   | 5.6 | Metho   | odology                                       |

|   |     | 5.6.1   | Hardware                                      |

|   |     | 5.6.2   | Operating System                              |

|   |     | 5.6.3   | Workload                                      |

|   |     | 5.6.4   | Virtual Machine Configuration                 |

|   |     | 5.6.5   | Measurement Methodology                       |

|   | 5.7 | Result  | s                                             |

|   |     | 5.7.1   | Single-Threaded Benchmarks                    |

|   |     | 5.7.2   | Scalable Multithreaded Benchmarks 91          |

|   |     | 5.7.3   | Non-scalable Multithreaded Benchmarks 95      |

|   | 5.8 | Summ    | nary                                          |

| 6 | Con | clusion | 97                                            |

|   | 6.1 |         | e Work                                        |

|   |     | 6.1.1   | WASH-assisted OS Scheduling                   |

|   |     | 6.1.2   | Heterogeneous-ISA AMP and Managed Software 99 |

|   |     |         |                                               |

**xiv** Contents

# **List of Figures**

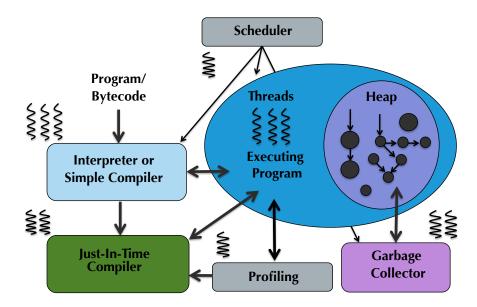

| 2.1  | Basic Virtual Machine and structure                                                                                                                                                                                                                                                                       | . 8  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

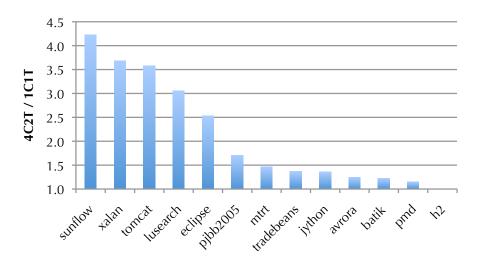

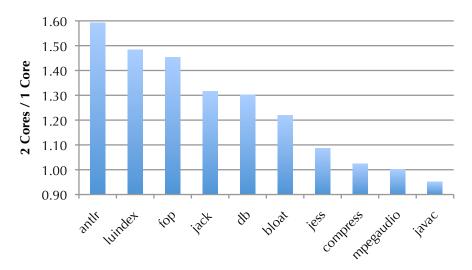

| 3.1  | Scalability of Java multithreaded benchmarks on i7 (45), comparing four cores with two SMT threads per core (4C2T) to one core with one SMT thread (1C1T)                                                                                                                                                 | . 20 |

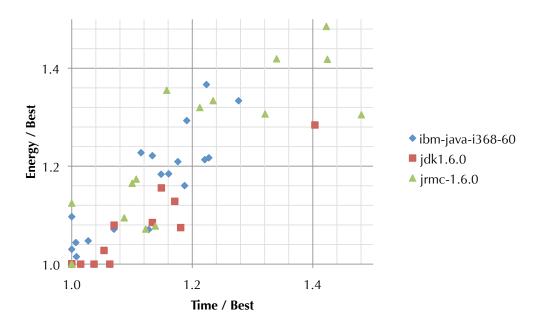

| 3.2  | The choice of JVM affects energy and performance. Benchmark time and energy on three different Java VMs on i7 (45), normalized to each benchmark's best result of the three VMs. A result of 1.0 reflect the best result on each axis.                                                                    | . 21 |

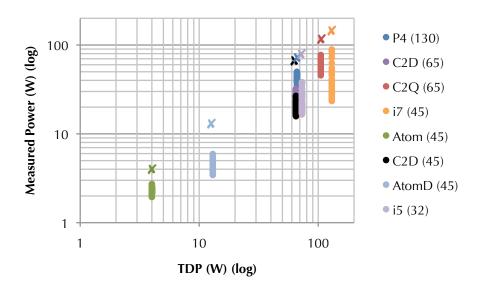

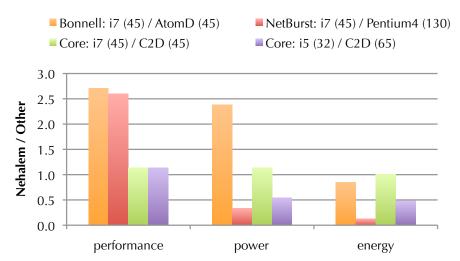

| 3.3  | Measured power for each processor running 61 benchmarks. Each point represents measured power for one benchmark. The 'X's are the reported TDP for each processor. Power is application-dependent and does not strongly correlate with TDP                                                                | . 28 |

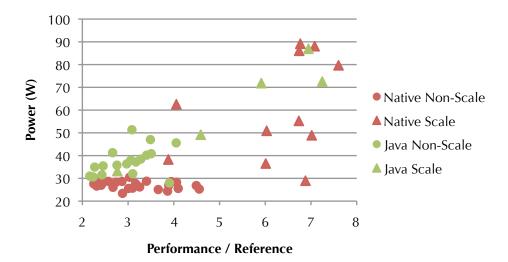

| 3.4  | Power / performance distribution on the i7 (45). Each point represents one of the 61 benchmarks. Power consumption is highly variable among the benchmarks, spanning from 23 W to 89 W. The wide spectrum of power responses from different applications points to power saving opportunities in software | . 29 |

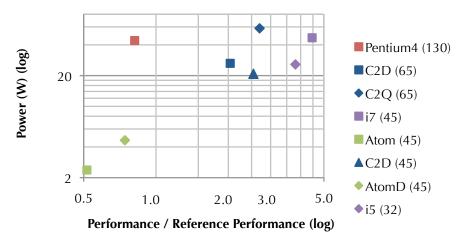

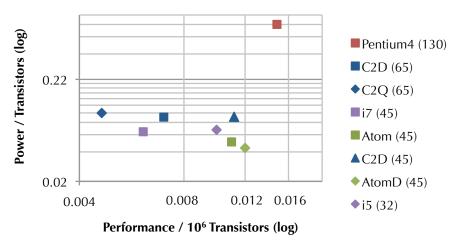

| 3.5  | Power / performance tradeoff by processor. Each point is an average of the four workloads. Power per million transistor is consistent across different microarchitectures regardless of the technology node. On average, Intel processors burn around 1 Watt for every 20 million transistors.            | . 30 |

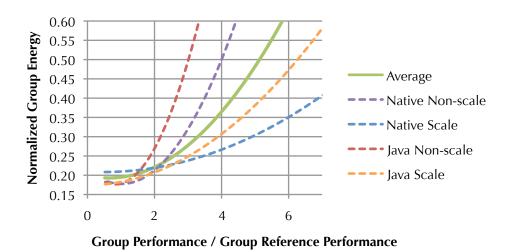

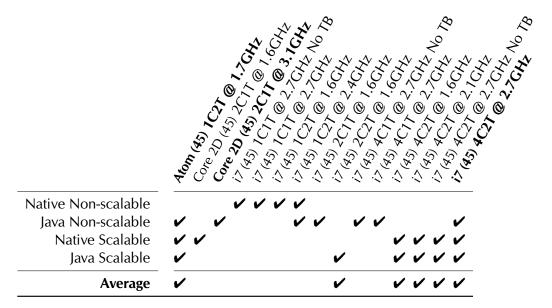

| 3.6  | Energy / performance Pareto frontiers (45 nm). The energy / performance optimal designs are application-dependent and significantly                                                                                                                                                                       |      |

| 3.7  | deviate from the average case                                                                                                                                                                                                                                                                             | . 32 |

| 3.8  | Scalability of single threaded Java benchmarks. Some single threaded Java benchmarks scale well. The underlying JVM exploits parallelism                                                                                                                                                                  |      |

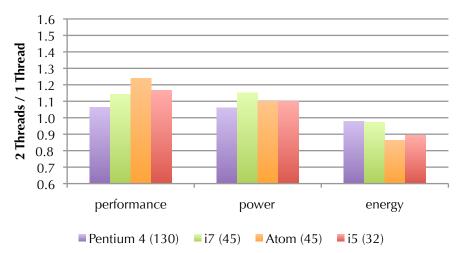

| 3.9  | for compilation, profiling and GC                                                                                                                                                                                                                                                                         | . 36 |

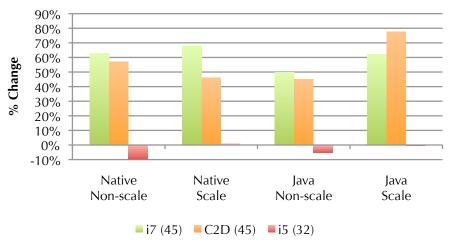

| 3 10 | cant energy savings on the recent i5 (32) and the in-order Atom (45) Clock: doubling clock in stock configurations. Doubling clock does                                                                                                                                                                   | . 37 |

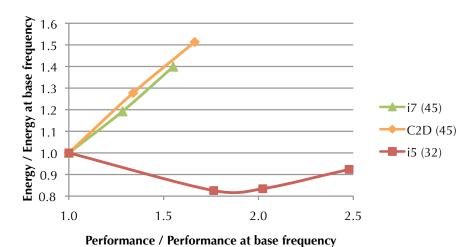

| 5.10 | not increase energy consumption on the recent i5 (32)                                                                                                                                                                                                                                                     | . 39 |

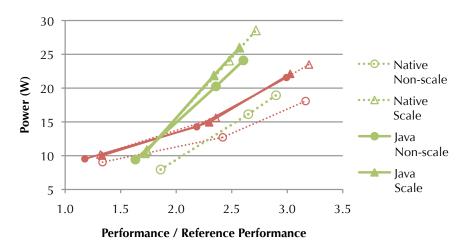

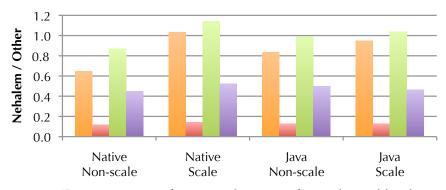

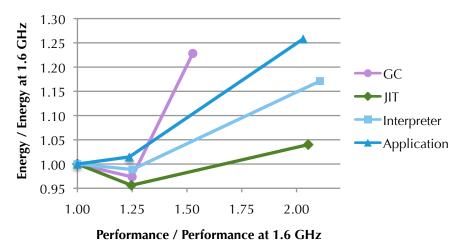

| 3.11 | Clock: scaling across the range of clock rates in stock configurations. Points are clock speeds.                                                                                                                                                                                                                                      | 40 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

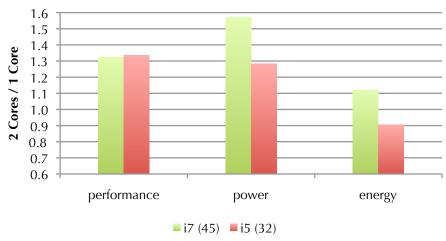

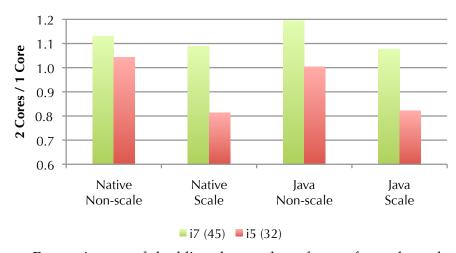

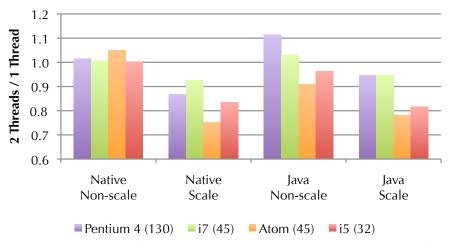

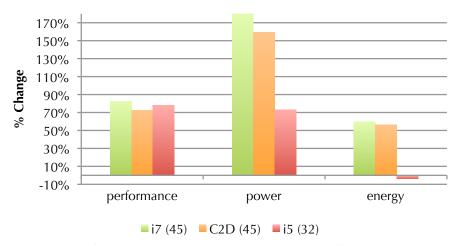

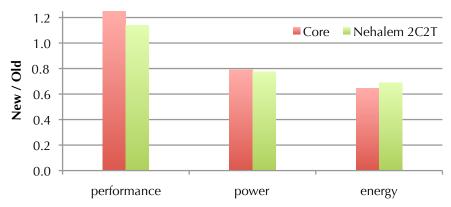

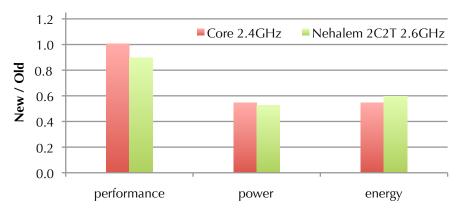

| 3.12 | Die shrink: microarchitectures compared across technology nodes. 'Core' shows Core 2D (65) / Core 2D (45) while 'Nehalem' shows i7 (45) / i5 (32) when two cores are enabled. Both die shrinks deliver substantial energy reductions                                                                                                  | 42 |

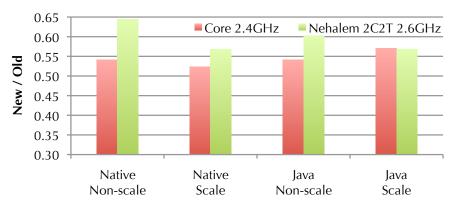

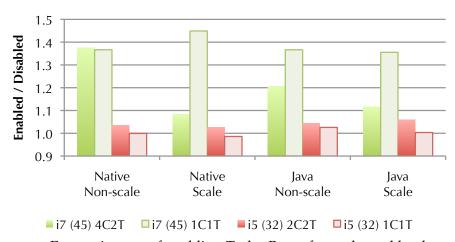

| 3.13 | Gross microarchitecture: a comparison of Nehalem with four other microarchitectures. In each comparison the Nehalem is configured to match the other processor as closely as possible. The most recent microarchitecture, Nehalem, is more energy efficient than the others, including the low-power Bonnell (Atom)                   | 44 |

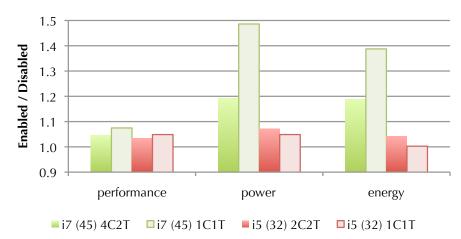

| 3.14 | Turbo Boost: enabling Turbo Boost on i7 (45) and i5 (32). Turbo Boost is not energy efficient on the i7 (45)                                                                                                                                                                                                                          | 46 |

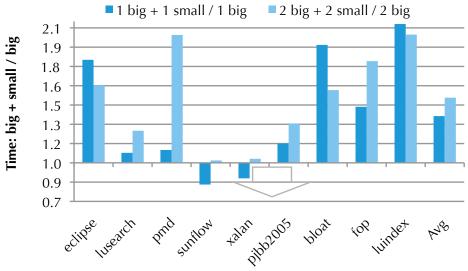

| 4.1  | Motivation: (a) VM services consume significant resources; (b) The naive addition of small cores <i>slows</i> down applications                                                                                                                                                                                                       | 50 |

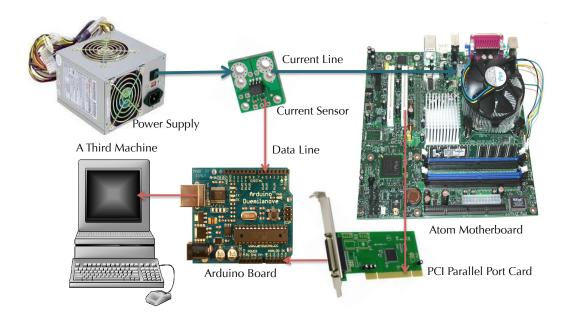

| 4.2  | Hall effect sensor and PCI card on the Atom                                                                                                                                                                                                                                                                                           | 54 |

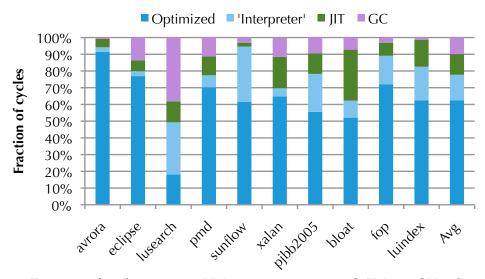

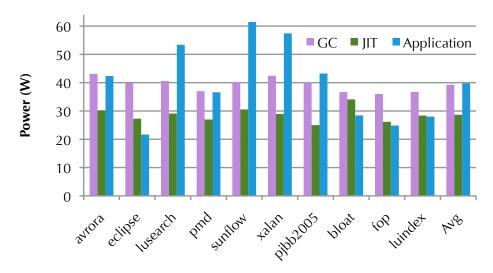

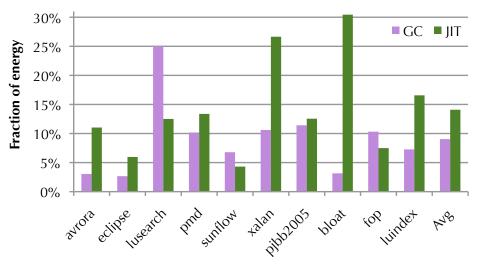

| 4.3  | GC, JIT, and application power and energy on i7 4C2T at 3.4 GHz using Jikes RVM. The power demands of the GC and JIT are relatively uniform across benchmarks. Together they contribute about 20% to total energy                                                                                                                     | 59 |

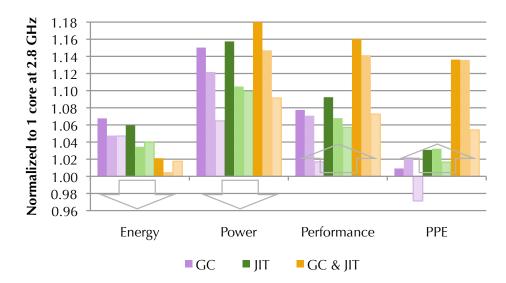

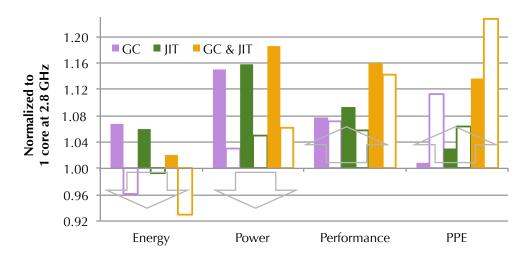

| 4.4  | Utility of adding a core dedicated to VM services on total energy, power, time, and PPE using Jikes RVM. Overall effect of binding GC, JIT, and both GC & JIT to the second core running at 2.8 GHz (dark), 2.2 GHz (middle), and 0.8 GHz (light) on the AMD Phenom II corrected for static power. The baseline uses one 2.8 GHz core | 61 |

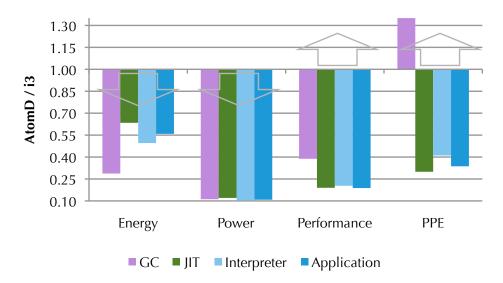

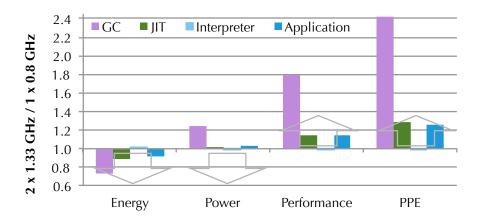

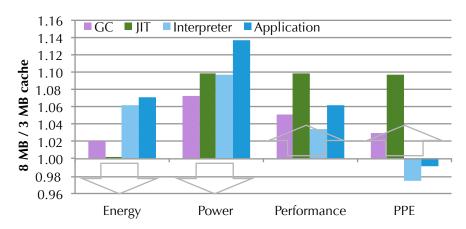

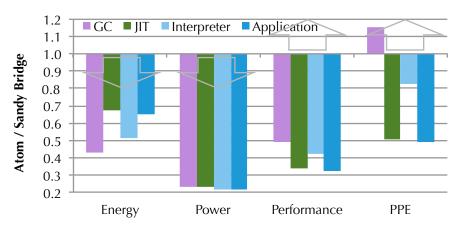

| 4.5  | Amenability of services and the application to an in-order-processor. GC, JIT, and interpreter use Jikes RVM. Interpreter uses HotSpot JDK, as stated in Section 4.2.5.3. These results compare execution on an in-order Atom to an out-of-order i3                                                                                   | 63 |

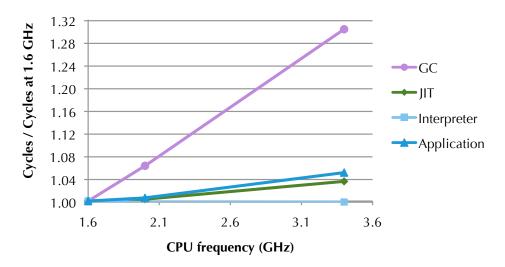

| 4.6  | Cycles executed as a function of clock speed, normalized to cycles at 1.6 GHz on the i7. GC, JIT, and interpreter use Jikes RVM. Interpreter uses HotSpot JDK, as stated in Section 4.2.5.3. The workload is fixed, so extra cycles are due to stalls                                                                                 | 63 |

| 4.7  | Microarchitectural characterization of VM services and application. GC, JIT, and interpreter use Jikes RVM. Interpreter uses HotSpot JDK, as stated in Section 4.2.5.3.                                                                                                                                                               | 66 |

| 4.8  | Microarchitectural characterization of VM services and application. GC, JIT, and interpreter use Jikes RVM. Interpreter uses HotSpot JDK, as stated in Section 4.2.5.3.                                                                                                                                                               | 67 |

| 4.9  | Modeling total energy, power, time, and PPE of an AMP system. The light bars show a model of an AMP with one 2.8 GHz Phenom II core and two Atom cores dedicated to VM services. The dark bars reproduce Phenom II results from Figure 4.4 that use a 2.8 GHz dedicated core for |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | VM services                                                                                                                                                                                                                                                                      | 69 |

| 4.10 | Adjusting the JIT's cost-benefit model to account for lower JIT execu-                                                                                                                                                                                                           |    |

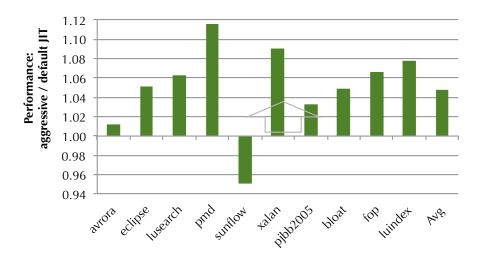

|      | tion costs yields improvements in total application performance                                                                                                                                                                                                                  | 70 |

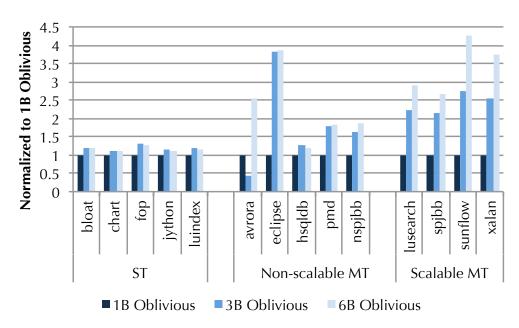

| 5.1  | Linux OS scheduler (Oblivious) on homogeneous configurations of a Phenom II normalized to one big core. We classify benchmarks as single threaded, non-scalable multithreaded (MT), and scalable MT.                                                                             |    |

|      | Higher is better                                                                                                                                                                                                                                                                 | 76 |

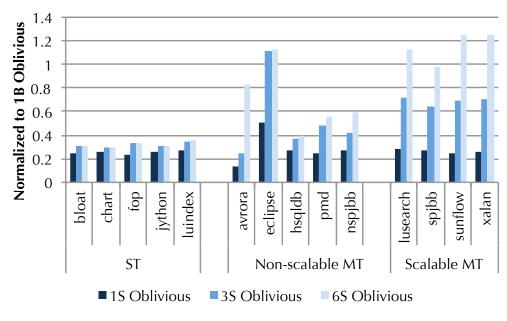

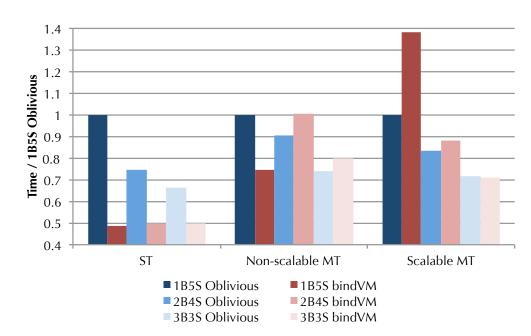

| 5.2  | Execution time of Oblivious and bindVM on various AMP configura-                                                                                                                                                                                                                 |    |

|      | tions, normalized to one 1B5S with Oblivious. Lower is better                                                                                                                                                                                                                    | 77 |

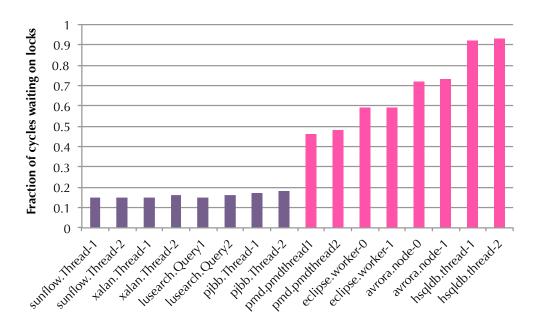

| 5.3  | Fraction of time spent waiting on locks as a ratio of all cycles per<br>thread in multithreaded benchmarks. The left benchmarks (purple) are<br>scalable, the right five (pink) are not. Low ratios are highly predictive                                                        |    |

|      | of scalability                                                                                                                                                                                                                                                                   | 79 |

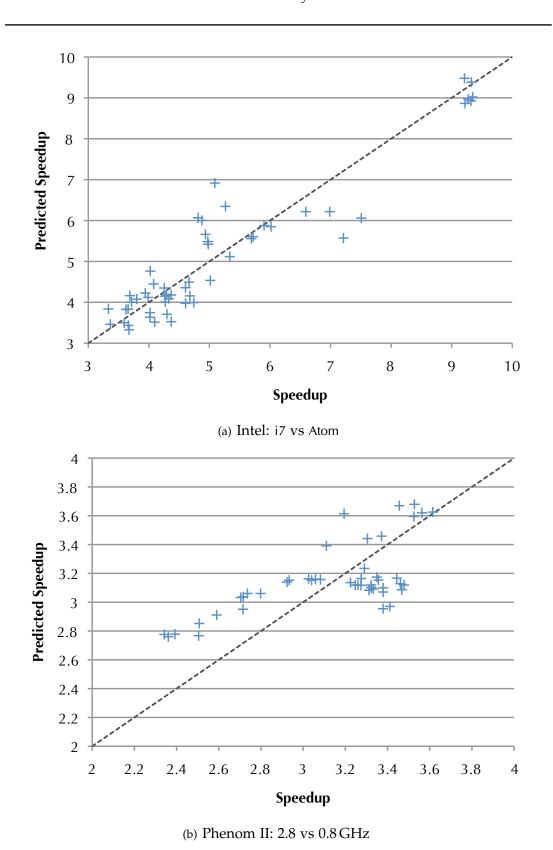

| 5.4  | Accurate prediction of thread core sensitivity. Y-axis is predicted. X-                                                                                                                                                                                                          |    |

|      | axis is actual speedup                                                                                                                                                                                                                                                           | 82 |

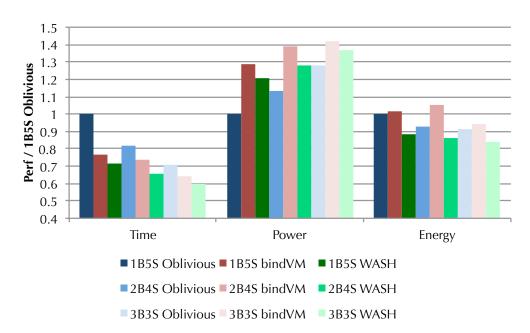

| 5.5  | All benchmarks: geomean time, power and energy with Oblivious,                                                                                                                                                                                                                   |    |

|      | bindVM, and WASH on all three hardware configurations. Lower is                                                                                                                                                                                                                  |    |

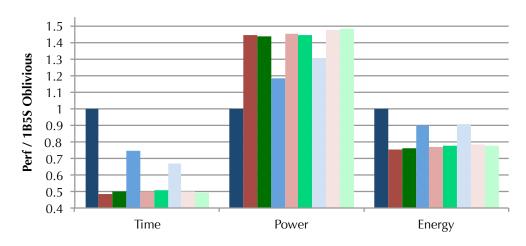

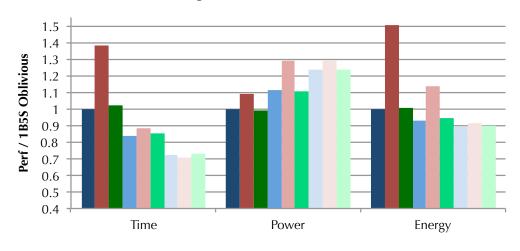

|      | better                                                                                                                                                                                                                                                                           | 89 |

| 5.6  | Normalized geomean time, power and energy for different benchmark                                                                                                                                                                                                                |    |

|      | groups                                                                                                                                                                                                                                                                           | 90 |

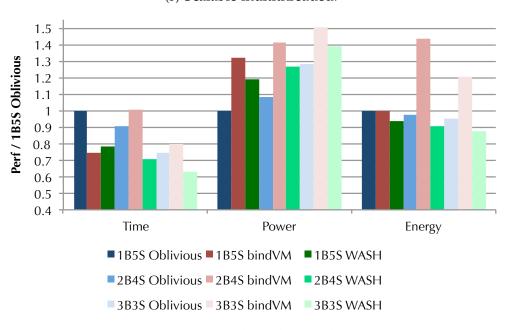

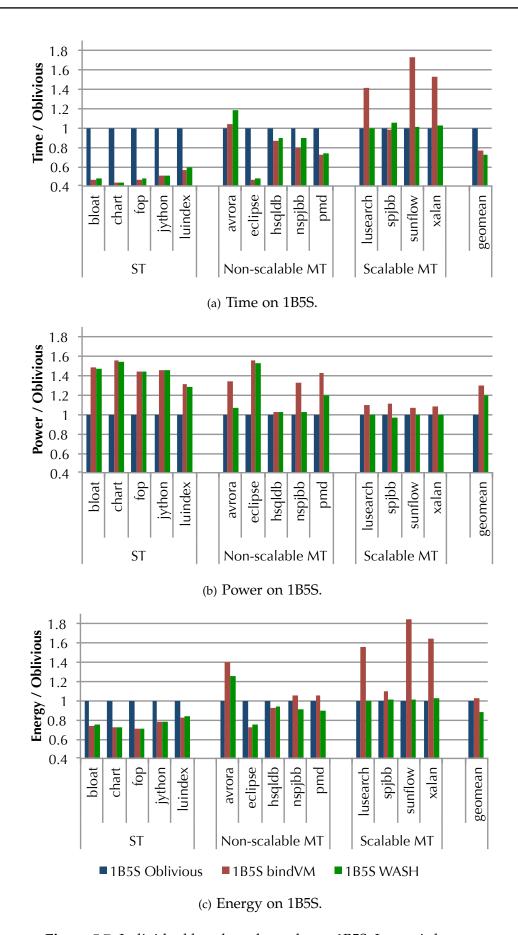

| 5.7  | Individual benchmark results on 1B5S. Lower is better                                                                                                                                                                                                                            | 92 |

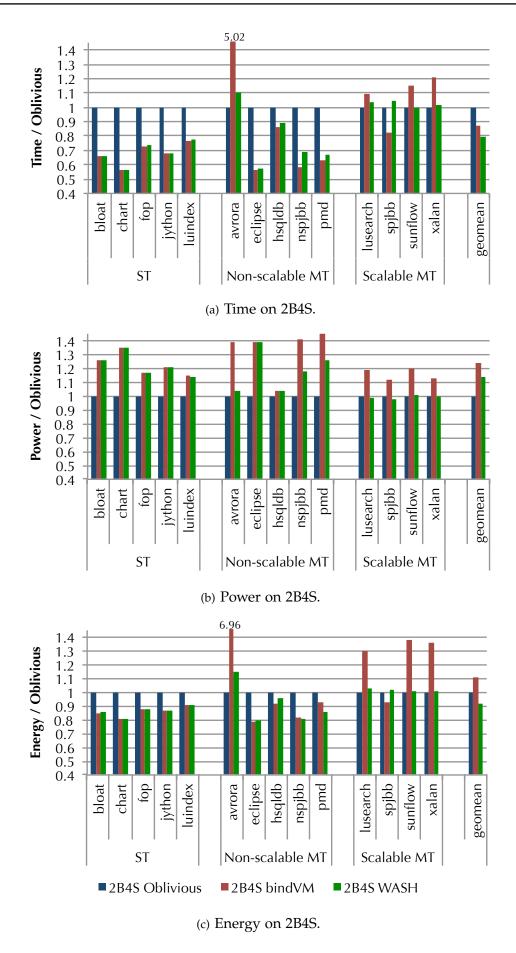

| 5.8  | Individual benchmark results on 2B4S. Lower is better                                                                                                                                                                                                                            | 93 |

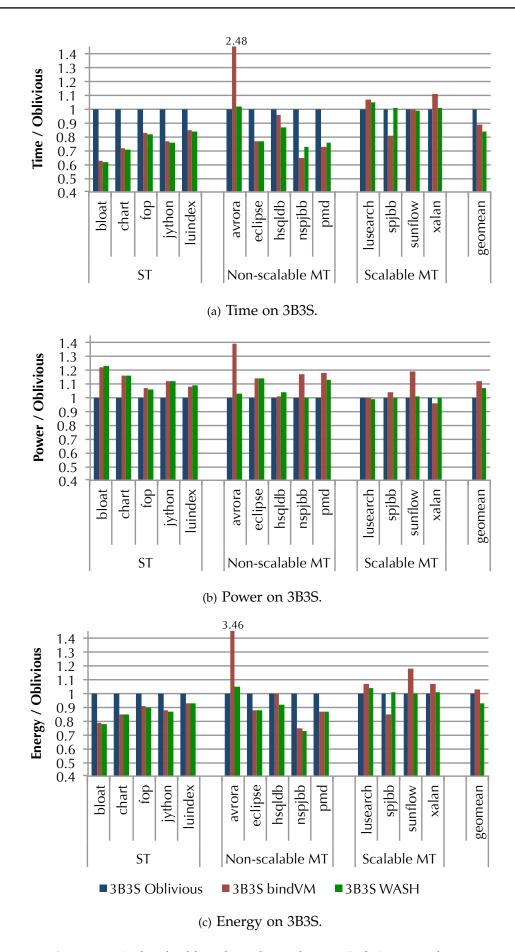

| 5.9  | Individual benchmark results on 3B3S. Lower is better                                                                                                                                                                                                                            | 94 |

## **List of Tables**

| 3.1 | Benchmark Groups; Source: SI: SPEC CINT2006, SF: SPEC CFP2006, PA: PARSEC, SJ: SPECjvm, D6: DaCapo 06-10-MR2, D9: DaCapo 9.12, and JB: pjbb2005.                                                                                                                                      | 17 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Experimental error. Aggregate 95% confidence intervals for measured execution time and power, showing average and maximum error across all processor configurations, and all benchmarks                                                                                               | 18 |

| 3.3 | The eight experimental processors and key specifications                                                                                                                                                                                                                              | 22 |

| 3.4 | Average performance characteristics. The rank for each measure is                                                                                                                                                                                                                     |    |

| 3.5 | indicated in small font. The machine list is ordered by release date Average power characteristics. The rank for each measure is indicated                                                                                                                                            | 25 |

|     | in small font. The machine list is ordered by release date                                                                                                                                                                                                                            | 25 |

| 3.6 | Findings. We organize our discussion around these eleven findings from an analysis of measured chip power, performance, and energy                                                                                                                                                    | 27 |

| 3.7 | on sixty-one workloads and eight processors                                                                                                                                                                                                                                           | 32 |

| 4.1 | Experimental processors                                                                                                                                                                                                                                                               | 53 |

|     |                                                                                                                                                                                                                                                                                       |    |

| 5.1 | Performance counters identified by PCA that most accurately predict thread core sensitivity. Intel Sandy Bridge simultaneously provides three fixed (F) and up to four other performance counters (V). AMD Phenom provides up to four performance counters                            | 81 |

| 5.2 | Experimental processors. We demonstrate generality of core sensitivity analysis on both Intel and AMD processors. Intel supports various clock speeds, but all cores must run at the same speed. All scheduling results for performance, power, and energy use the Phenom II since it |    |

| 5.3 | supports separate clocking of cores, mimicking an AMP                                                                                                                                                                                                                                 | 87 |

|     | classified as either single threaded, non-scalable or scalable                                                                                                                                                                                                                        | 88 |

## Introduction

This thesis addresses the problem of executing managed software on heterogeneous hardware efficiently and transparently.

#### 1.1 Problem Statement

In the past decade, computer architecture design changed from being limited by transistors to being limited by power. While transistor numbers are still scaling up under Moore's law, the CMOS threshold voltage set by leakage current is not scaling down accordingly. As a consequence, under a limited power budget, the fraction of a chip that can be powered at full speed at one time is decreasing [Esmaeilzadeh et al., 2011a]. An obvious example is the use of Intel Turbo Boost technique [Intel, 2008]. The technique will power portions of the transistors on a chip at higher frequency while the other transistors are powered off. Another indication is that even as the transistor size has shrunk in each recent generation, the CPU frequency has not increased accordingly. Apart from power constraints, energy cost is also a serious issue in PC, server, and portable device markets. Globally, data centers are estimated currently to consume about US\$30B worth of electricity per year [Piszczalski, 2012]. Power and energy problems in all market sectors are redefining the road for architecture development.

Heterogeneous hardware is recognised by academia and industry as a promising approach to exploit the abundant transistors of a chip for performance improvement under a limited power budget. It can accelerate the serial phases of applications on a few big cores and the parallel phases on many small cores. Some cores can be tailored for specific purposes. Kumar et al. model a single-ISA asymmetric multicore architecture [Kumar et al., 2003]. By running applications on the most appropriate cores, they reduce the total energy by 40%. Morad et al. show theoretically that single-ISA asymmetric multiprocessors can reduce power consumption by more than two thirds with similar performance compared to symmetric multiprocessors [Morad et al., 2006]. Vendors are building Asymmetric Multicore Processors (AMPs) already, such as ARM's big.LITTLE [Greenhalgh, 2011], Intel QuickIA [Chitlur et al., 2012], and NVIDIA Tegra 4 [NVIDIA, 2013]. However, heterogeneous processors expose hardware complexity to software developers. Without software support, the hetero-

Introduction

geneous hardware will not be able to deliver on its promise.

The software community is facing orthogonal challenges of a similar magnitude, with major changes in the way software is deployed, sold, and interacts with hardware. Developers are increasingly choosing managed languages, sacrificing performance for programmer productivity, time-to-market, reliability, security, and portability. Smart phone and tablet applications are predominantly written in managed languages. Modern web services combine managed languages, such as PHP on the server side and JavaScript on the client side. In markets as diverse as financial software and cell phone applications, Java and .NET are the dominant choices. Until recently the performance overheads associated with managed languages were made tolerable by an exponential growth in sequential hardware performance. Unfortunately, this source of mitigation is drying up just as managed languages are becoming ubiquitous.

The hardware and software communities are thus both facing significant change and major challenges.

### 1.2 Scope and Contributions

The aim of my research is to mitigate the two major challenges happening in the software and hardware worlds—to explore the potential efficiency of heterogeneous processors while insulating software from this complexity.

There are generally two categories of heterogeneous architectures: those that integrate main cores with accelerators for specific domains (graphics, imaging, security, speech, etc.) and those that integrate general purpose cores which are normally based on the same ISA family but asymmetric in performance and power characteristics. Single-ISA AMPs allow threads to be scheduled between different core types, and do not necessarily force the redesign of existing software. The single-ISA AMP is the focus of my thesis. I use Java workloads as the representative of managed software, since Java has mature virtual machines and sophisticated benchmarks. While specific quantitative results may vary, the methodologies should be applicable to other managed languages.

Power measurement and analysis. To exploit the power, energy, and performance response of different hardware features running with various workloads on real processors, this thesis is the first to quantitatively study measured power and performance at the chip level across hardware generations, comparing managed against native workloads according to different hardware characteristics. The quantitative data reveals thirteen hardware or software findings. Two themes emerge: (1) energy efficient architecture design (i.e. less energy for the same task since a pure "race to finish" measure is not sufficient as it can use disproportionate amounts of power) is very sensitive to workload type (native or managed), and (2) each hardware feature elicits a different power and performance response. The variations in responses and the opportunity to mix them

motivate the exploration of managed software optimization combined with the use of AMPs.

AMPs and VM services. Researchers often examine the challenges of hardware and software in isolation. This thesis uses novel hardware/software co-design methodologies to solve the challenges together. Heterogeneous hardware will only be practical if it is transparent to application software. If every new generation of hardware requires application developers to change their code, developers are very unlikely to have the time or expertise to use it. This thesis shows that Virtual Machine (VM) services, such as garbage collection and just-in-time compilation, can exploit the potential efficiency of AMPs transparently to applications by running on the small cores. VM services understand and abstract the hardware. The tailored small cores of AMPs can hide the VM services overheads and improve total efficiency without any changes to applications.

Managed software scheduler for AMPs. To fully explore the efficiency of AMPs and abstract over the complexity, we consider the problem of scheduling managed application threads on AMPs. Managed applications consist of a *mess* of heterogeneous threads with different functions and amounts of work compared to classic scalable parallel workloads written in native languages. This thesis presents a dynamic scheduling algorithm called WASH (Workload Aware Scheduler for Heterogeneity). WASH can be integrated in managed language VMs to manage parallelism, load balance, and core sensitivity for both managed application and VM service threads. We show that WASH achieves substantial performance and energy improvements.

In summary, this thesis addresses the interaction of modern software with emerging hardware. It shows the potential of exploiting the VM abstraction layer to hide hardware complexity from applications, and at the same time exploiting the differentiated power and performance characteristics to substantially improve performance and energy efficiency.

### 1.3 Thesis Outline

The body of the thesis is structured around the three key contributions outlined above and starts with related work.

Chapter 2 discusses emerging AMPs and their potential for solving the power crisis. It presents the related work that proposes to deliver the potential efficiency of AMPs by scheduling threads to appropriate core types. It introduces a main source of overhead in managed software—VM services, as well as the relevant literature that attacks those overheads.

Chapters 3, 4, and 5 comprise the main body of the thesis, covering the three key contributions. Chapter 3 systematically analyzes the power, performance, and energy responses of managed software compared with native software, and a variety of hardware features across five technology generations. For native software, we

4 Introduction

use SPEC CPU2006 and PARSEC as workloads. For managed software, we use SPECjvm, DaCapo and pjbb2005 as workloads. Chapter 4 identifies the complimentary relationship of AMP and VM services, which can hide each other's disadvantages—complexity and overheads, and exploit each other's advantages—efficiency and abstraction. Chapter 5 describes a new dynamic VM scheduler which schedules both managed application and VM threads to different core types of AMPs to improve efficiency. In both Chapter 4 and 5, we use DaCapo and pjbb2005 as managed workloads.

Finally, Chapter 6 concludes the thesis, summarizing how my contributions have identified, quantified, and addressed the challenges of managed software and AMP architectures. It further identifies key future research directions for emerging hardware and software.

## **Background and Related Work**

This thesis explores the interplay of Asymmetric Multicore Processors (AMPs) and managed software. This chapter provides the background information about the increasing necessity of AMP architectures and how to utilise them for efficiency. Section 2.1 introduces AMP architectures and the techniques to expose their potential energy and performance efficiency. It also explains how Virtual Machines (VMs) support managed software abstractions and ways to reduce the VM overheads. Section 2.2 provides an overview of VMs, with an emphasis on the three major services—the Garbage Collector (GC), the Just-In-Time compiler (JIT), and the interpreter.

### 2.1 Single-ISA Asymmetric Multicore Processors

This thesis focuses on single-ISA AMP architectures. This design consists of cores with the same ISA (instruction set architecture), but different microarchitectural features, speed, and power consumption. The single-ISA AMP architecture was proposed by Kumar et al. [2003] to reduce power consumption. The motivation is that different applications have different resource requirements during their execution. By choosing the most appropriate core from available cores from different points in the power and performance design space, specific performance and power requirements can be met. Morad et al. show that in theory single-ISA AMP architectures can reduce power consumption by more than two thirds with similar performance compared to symmetric multiprocessors [Morad et al., 2006]. Single-ISA AMP architectures can be constructed using a set of previously-designed processors with appropriately modified interfaces, thus reducing the design effort required. For example, Intel QuickIA integrates Xeon 5450 and Atom N330 as the big and small cores via the FSB (front side bus) [Chitlur et al., 2012]. ARM's big.LITTLE system connect the Cortex-A15 and Cortex-A7 as the big and small cores via the CCI-400 coherent interconnect [Greenhalgh, 2011]. Also, code can migrate among different cores without recompilation. However, AMP architectures cannot deliver on the promise of efficiency without software assistance to schedule threads to appropriate cores. The following subsection will discuss current proposals to utilize AMP architectures.

#### 2.1.1 AMP Utilization

Several AMP schedulers are proposed in previous work. Most of them make scheduling decisions according to the thread's microarchitecture characteristics [Saez et al., 2011, 2012; Craeynest et al., 2012; Kumar et al., 2004; Becchi and Crowley, 2006], while others do not [Li et al., 2007; Mogul et al., 2008; Saez et al., 2010]. We will discuss them separately in the following text.

For those algorithms considering the thread's microarchitecture characteristics, the fundamental property for making scheduling decisions is speedup factor, that is, how much quicker a thread retires instructions on a fast core relative to a slow core [Saez et al., 2012]. Systems either measure or model the speedup factor. To directly determine speedup, the system runs threads on each core type, getting their IPC directly [Kumar et al., 2004; Becchi and Crowley, 2006]. To model the speedup, the system uses thread characteristics such as cache-miss rate, pipeline-stall rate and the CPU's memory-access latency. This information can be either gathered online by performance counters [Saez et al., 2011, 2012; Craeynest et al., 2012], or offline by using a reuse-distance profile [Shelepov et al., 2009]. By contrast to direct measurements, modelling does not need to migrate threads among different core types before making scheduling decisions.

Saez et al. gather memory intensity (cache miss rate) information online to model the speedup while they use an AMP platform with cores only differing in clock speed [Saez et al., 2011]. More recently, they consider an AMP composed of cores with different microarchitectures [Saez et al., 2012]. They change the retirement width of several out-of-order cores in a system to model the behaviour of in-order cores, while the other cores use their default settings. They use an additive regression technique from the WEKA machine learning package to find out the performance counters that contribute more significantly to the resulting speedup factor, which are IPC, LLC miss rate, L2 miss rate, execution stalls and retirement stalls. The modeled speedup will be the linear combination of those performance counter values with their additive-regression factors. Craeynest et al. consider cores with different microarchitecture too and use MLP and ILP information to estimate CPI for different core types [Craeynest et al., 2012]. They calculate MLP from LLC misses rate, big core reorder buffer size, and average data dependancy distance. They calculate ILP from instruction issue width and the probability of executing a certain number of instructions in a given cycle on the small cores.

There are several algorithms oblivious to the thread's microarchitecture characteristics. Li et al. propose a scheduling algorithm to ensure the load on each core type is proportional to its computing power and to ensure fast-core-first, which means threads run on fast cores whenever they are under-utilised [Li et al., 2007]. This algorithm does not consider which threads can benefit the most from the big cores' resources. Mogul et al. schedule frequently used OS functions to small cores [Mogul et al., 2008]. This algorithm can only benefit OS-intensive workloads. Saez et al. dynamically detect the parallelism of applications [Saez et al., 2010]. If the number of runnable threads of an application is higher than a threshold, the threads of this ap-

plication will primarily run on the slow cores. Otherwise those threads will primarily run on fast cores.

Whether or not the scheduling decisions can be changed while the threads run determines whether the AMP algorithm is *static* or *dynamic*. *Static* means threads will not be migrated again once decisions are made [Kumar et al., 2004; Shelepov et al., 2009; Saez et al., 2011], while *dynamic* adapts when thread behaviours change [Becchi and Crowley, 2006; Saez et al., 2012] or there is CPU load imbalance [Li et al., 2007]. For dynamic algorithms, the interval for sampling and migrating affects the performance, since migration can increase cache misses, especially for NUMA systems. Li et al. analyze the migration overhead and use a resident-set-based algorithm to predict the overhead before migration [Li et al., 2007].

Recent work also proposes to schedule critical sections to big cores in AMP architectures [Du Bois et al., 2013; Joao et al., 2012, 2013]. Du Bois et al. use a criticality time array with each entry for each thread to work out which one is the most critical thread [Du Bois et al., 2013]. After each time interval, the hardware will divide the time by active thread numbers in that period and add the value to the criticality time array. The thread with the highest value in the array will be the critical thread, and will be scheduled to the big cores. Joao et al. measure the cycles of threads having to wait for each bottleneck, and accelerate the most critical section on the big cores of the AMP architecture [Joao et al., 2012]. Their approach requires the programmer, compiler or library code to insert specific instructions to the source code, assisting hardware to keep track of the bottlenecks. Subsequently, they extend their work to detect threads that execute longer than other threads and put them on the big cores too [Joao et al., 2013]. They evaluate the results by using both a single multithreaded application and multiple multithreaded applications running concurrently. However, they always set the total number of threads equal to the number of cores.

The AMP scheduler proposed in this thesis schedules threads based on not only the number of threads, but also the scalable or non-scalable parallelism exhibited by those threads. It dynamically accelerates the critical thread and shares resources as appropriate. The prior algorithms do not consider scheduling appropriate threads on slower cores for energy efficiency, while our scheduler exploits to gain energy efficiency, especially for threads that are not on the critical path. Furthermore, none of the prior work considers application and VM service threads together.

## 2.2 Managed Language Virtual Machines

This section provides some background on modern virtual machines for managed languages. Figure 2.1 shows the basic VM structure. While executing managed software, the VM uses dynamic interpretation and JIT compilation to translate standardised portable bytecode to the binary code of the target physical machine. The JIT uses dynamic profiling to optimize frequently executed code for performance. The GC automatically reclaims memory not in use anymore. There are some other VM services too, such as a scheduler and finalizer. Most of those VM services are

Figure 2.1: Basic Virtual Machine and structure.

multithreaded, asynchronous, non-critical and have their own hardware behaviour characteristics. This thesis will focus on the three main services: GC, JIT, and interpreter.

There are several mature Java VMs, such as Oracle's Hotspot, Oracle's JRockit, IBM's J9, and Jikes RVM [Alpern et al., 2005; The Jikes RVM Research Group, 2011]. This thesis mainly uses Oracle's Hotspot, the most widely used production JVM, and Jikes RVM, the most widely used research JVM.

#### 2.2.1 Garbage Collector

Managed languages use GC to provide memory safety to applications. Programmers allocate *heap* memory and the GC automatically reclaims it when it becomes unreachable. GC algorithms are graph traversal problems, amenable to parallelization, and fundamentally memory-bound. There are several canonical GC algorithms, such as reference counting, mark-sweep, semi-space and mark-region. The following paragraphs will introduce the GCs used in this thesis.

Mark-region collectors divide the heap into fixed sized regions. The collectors allocate objects into free regions and reclaim regions containing no live objects. The best performing example of a mark-region algorithm is Immix [Blackburn and McKinley, 2008]. It uses a hierarchy of blocks and line regions, in which each block consists of some number of lines. Objects may cross lines but not blocks. Immix recycles partly used blocks by reclaiming at a fine-grained line granularity. It uses lightweight opportunistic evacuation to address fragmentation and achieves space efficiency, fast collection, and continuous allocation for application performance.

Production GCs normally divide the heap into spaces for objects of different ages, which are called generational GCs [Lieberman and Hewitt, 1983; Ungar, 1984; Moon,

1984]. The generational hypothesis states that most objects have very short lifetimes, therefore generational GCs can attain greater collection efficiency by focusing collection effort on the most recently allocated objects. The youngest generation is normally known as the *nursery* and the space containing the oldest objects is known as the *mature space*. Different collection policies can be applied to each generation. For example, Jikes RVM uses a generational collector with an evacuating nursery and an Immix mature space for its production configuration. The default collector for Oracle Hotspot uses an evacuating nursery, a pair of semi-spaces as the second generation, and a mark-sweep-compact mature space. Generational GCs are very effective. The majority of collectors in practical systems are generational.

There are *stop-the-world* and *concurrent* GCs, depending on whether the application execution halts or not during a collection. As the application halts and guarantees not to change the object graph while a collection, stop-the-world GC is simpler to implement and faster than concurrent GC. However, it is not suited to real-time or interactive programs where application pauses can be unacceptable. Concurrent GC is designed to reduce this disruption and improve application responsiveness. For concurrent GC, both collector and application threads are running simultaneously and synchronize only occasionally. Many concurrent collectors have been proposed, see for example [Ossia et al., 2002; Printezis and Detlefs, 2000; O'Toole and Nettles, 1984]. The concurrent mark-sweep collector in Jikes RVM uses a classic snapshot-at-the-beginning algorithm [Yuasa, 1990].

#### 2.2.2 Just-In-Time Compiler

High performance VMs use a JIT to dynamically optimize code for frequently executed methods and/or traces. Because the code will have already executed at the time the optimizing JIT compiles it, the runtime has the opportunity to dynamically profile the code and tailor optimizations accordingly. The JIT will compile code asynchronously with the application and may compile more than one method or trace at once.

Compilation strategies may be incrementally more aggressive according to the heat of the target code. Thus, a typical JIT will have several optimization levels. The first level may apply register allocation and common sub-expression elimination and the second level applies optimizations that require more analysis, e.g., loop invariant code motion and loop pipelining. The compiler also performs feedback-directed optimizations. For example, it chooses which methods to inline at polymorphic call sites based on the most frequently executed target thus far. Similarly, it may perform type specialization based on the most common type, lay out code based on branch profiles, and propagate run-time constant values. These common-case optimizations either include code that handles the less frequent cases or that falls back to the interpreter or recompiles when the assumptions fail.

Each system uses a cost model that determines the expected cost to compile the code and the expected benefit. For example, the cost model used in Jikes RVM uses the past to predict the future [Arnold et al., 2000]. Offline, the VM first computes

compiler DNA: (1) the average compilation cost as a function of code features such as loops, lines of code, and branches, and (2) average improvements to code execution time due to the optimizations based on measurements on a large variety of code. The compiler assumes that if a method has executed for 10% of the time thus far, it will execute for 10% of the time in the future. At run time, the JIT recompiles a method at a higher level of optimization if the predicted cost to recompile it at that level and the reduction in the method execution time will reduce total time.

#### 2.2.3 Interpreter

Many managed languages support dynamic loading and do not perform ahead-of-time compilation. The language runtime must consequently execute code immediately, as it is loaded. Modern VMs use interpretation, template compilation to machine code, or simple compilation without optimizations (all of which we refer to as interpretation for convenience). An interpreter is thus highly responsive but offers poor code quality. Advanced VMs will typically identify frequently executed code and dynamically optimize it using an optimizing compiler. In steady state, performance-critical code is optimized and the remaining code executes via the interpreter. One exception is the .NET framework for C#, which compiles all code with many optimizations immediately, only once, at load time. The interpreter itself is not parallel, but it will reflect any parallelism in the application it executes.

#### 2.2.4 VM Overhead

This section will introduce the related work on studying overheads of VM services and how to reduce those overheads while improving managed software performance. Most of the works focus on improving the software algorithm or building specific hardware for that purpose. There are few works focusing on fulfilling the task through utilizing the available hardware efficiently.

#### 2.2.4.1 VM Performance Overhead Studies

There have been many studies analyzing and optimizing the performance overheads of VM services since the earlier days of language VMs such as Lisp interpreter [McCarthy, 1978], SmallTalk VM [Deutsch and Schiffman, 1984] and others. Here we summarize some of the more recent relevant papers.

Arnold et al. describe the adaptive optimization system of Jikes RVM [Arnold et al., 2000]. The system uses low-overhead sampling technique to drive adaptive and online feedback-directed multilevel optimization. The overhead of this optimization system is 8.6% in start-up period and 6.0% for long-running period (accumulative timings of five runs for the same benchmark) using SPECjvm98.

Ha et al. introduce a concurrent trace-based JIT that use novel lock-free synchronization to trace, compile, install, and stitch traces on a separate core to improve responsiveness and throughput [Ha et al., 2009]. It also opens up the possibility of

increasing the code quality with compiler optimizations without sacrificing the application pause time. The paper shows the interpreter and JIT time in Tamarin-Tracing VM using the SunSpider JavaScript benchmark suite. When using sequential JIT, the compilation time ranges from 0.2% to 24.6% and the range for interpreter is 0.4% to 58.0%. By using concurrent JIT, the throughput can increase 5% on average and up to 36%.

Blackburn et al. give detailed performance studies of three whole heap GCs and generational counterparts: semi-space, mark-sweep and reference counting [Blackburn et al., 2004]. They measure the GC and application execution time for different benchmarks as a function of heap size for different GC algorithms. They also evaluate the impact of GC on application's cache locality. The conclusions from experiments include that (1) GC and total execution time are sensitive to heap size; (2) generational GC performs much better than their whole heap variants; and (3) the contiguous allocation of collectors attains significant locality benefits over free-list allocators.

#### 2.2.4.2 VM Energy Overhead Studies

In contrast to the number of studies conducted into performance, there are fewer studies that evaluate power and energy overhead of VM services.

Chen et al. study mark-sweep GC using an energy simulator and the Shade SPARC simulator, which is configured to be a cacheless SoC [Chen et al., 2002]. They use embedded system benchmarks, ranging from utility programs used in hand-held devices to wireless web browser to game programs. Their results show that the GC costs 4% in total energy. They also develop a mechanism to improve leakage energy by using a GC-controlled optimization to shut off memory banks without live data.

Velasco et al. study the energy consumption of state-of-the-art GCs (e.g., mark-sweep, semi-space, and generational GC) and their impact on total energy cost for designing embedded systems [Velasco et al., 2005]. They use Jikes RVM, Dynamic SimpleScalar (DSS) [Huang et al., 2003], and combine DSS with a CACTI energy/de-lay/area model to calculate energy. Their energy simulation results follow the performance measurements from prior work [Blackburn et al., 2004]. They use SPECjvm98 benchmarks and divide the benchmarks into three scenarios: limited memory use, C-like memory use, and medium to high amounts of memory use. For the second scenario, the copying collector with mark-sweep gets the best energy results and the generational GC achieves the best for the third scenario. However, their results show GC costs 25% to 50% in the second and third scenarios, which is a big contrast with prior results.

Hu and John evaluate the performance and energy overhead of GC and JIT compilation, and their impact on application energy consumption on a hardware adaption framework [Hu et al., 2005] implemented with DSS and Jikes RVM [Hu and John, 2006]. In their evaluation, for SPECjvm benchmarks, JIT costs around 10% in total on average. GC costs depend on the heap size, ranging from 5% to 18% on average. By using the adaptive framework, they study the preferences of configurable units

(issue queue, reorder buffer, L1 and L2 caches) on the JIT and GC. Their results show that GCs prefer simple cores for energy efficiency. GCs can use smaller cache, issue queue, and reorder buffer with minimal performance impact. A JIT requires larger data caches than normal applications, but smaller issue queues and reorder buffers.

While the work described above uses simulators, our work measures the power and energy overhead of GC and JIT on real machines. The interpreter's power and energy overhead was not measured due to the sampling frequency limitations of the measurement hardware.

#### 2.2.4.3 Hardware Support for GC

There exist many proposals for hardware supported GC [Moon, 1985; Ungar, 1987; Wolczko and Williams, 1992; Nilsen and Schmidt, 1994; Wise et al., 1997; Srisa-an et al., 2003; Meyer, 2004, 2005, 2006; Stanchina and Meyer, 2007b,a; Horvath and Meyer, 2010; Click et al., 2005; Click, 2009; Cher and Gschwind, 2008; Maas et al., 2012; Bacon et al., 2012]. The goals for this work are mainly to eliminate GC pauses and improve safety, reliability, and predictability. Some works aim to have a better use of the available hardware by offloading GC to it.

The first use of hardware to support GC was in Lisp machines [Moon, 1985]. In those machines, special microcode accompanies the implementation of each memory fetch or store operation. The worst-case latencies are improved, but the runtime overhead and the throughput are not improved. The following projects, Smalltalk on a RISC (SOAR) [Ungar, 1987] and Mushroom [Wolczko and Williams, 1992], target improving the throughput, but not the worst-case latencies of GC. At that time, since the target audience was small for such special-purpose architectures, major software developers did not consider it economical to port their products to specialized architectures.

Starting in the 1990s, to avoid the pitfalls of special purpose machines, researchers proposed active memory modules with hardware support for GC, including Nilsen and Schmidt's garbage collected memory module [Nilsen and Schmidt, 1994], Wise et al.'s reference count memory [Wise et al., 1997] and Srisa-an et al.'s active memory processor [Srisa-an et al., 2003]. This technology investment may be shared between users of many different processor architectures. However, the hardware cost for the memory module is relatively high and depends on the size of the garbage collected memory.

Meyer's group published a series of works exploring hardware support for GC [Meyer, 2004, 2005, 2006; Stanchina and Meyer, 2007b,a; Horvath and Meyer, 2010]. They initially developed a novel processor architecture with an object-based RISC main core and a small, microcoded on-chip GC coprocessor. Because of the tight coupling of processor and collector, all synchronization mechanisms for real-time GC are efficiently realized in hardware. Both read barrier checking and read barrier fault handling are entirely realized in hardware [Meyer, 2004, 2005, 2006]. Based on this initial system, they then introduced a hardware write barrier for generational GC to detect inter-generational pointers and execute all related book-keeping operations

entirely in hardware. The runtime overhead of generational GC is reduced to near zero [Stanchina and Meyer, 2007a]. In recent work, they developed a low-cost multicore GC coprocessor to solve the synchronization problem for parallel GCs [Horvath and Meyer, 2010].

Azul Systems built a custom chip to run Java business applications [Click et al., 2005; Click, 2009]. They redesigned about 50% of the CPU and built their own OS and VM. The chips have special support for read and write barriers, fast user-mode trap handlers, cooperative pre-emption, and special TLB support, which enable a highly concurrent, parallel and compacting GC algorithm capable of handling very large heaps and large numbers of processors.

Several proposals use specialized processing units designed for something else to run GC. Cher and Gschwind offload the mark phase to the SPE co-processor on a Cell system [Cher and Gschwind, 2008]. Maas et al. offload GC to a GPU, motivated by the observation that consumer workloads often underutilize GPU and create an opportunity to offload some system tasks to GPU [Maas et al., 2012]. They show a new algorithm, and variations thereof, for performing the mark phase of a mark-sweep GC on the GPU by using a highly parallel queue-based breadth-first search. They use an AMD APU integrating CPU and GPU into a single device as a test platform. The performance result of this GPU-based GC turns out to be 40 to 80% slower than CPU-based collector, partly because of the large data transfer overhead between the CPU and GPU, and the limited memory space for the GPU.

In very recent work, Bacon et al. implement the first complete GC in hardware (as opposed to hardware-assist or microcode) [Bacon et al., 2012]. By using a concurrent snapshot algorithm and synthesising it into hardware, the collector provides single-cycle access to the heap and never stalls the mutator for a single cycle. Compared to the work before, the CPU does not need modification, and also the heap size does not need to be larger than the maximum live data. However, they trade flexibility in memory layout for large gains in collector performance. The shape of the objects (the size of the data fields and the location of pointers) is fixed. Results show this complete hardware GC achieves higher throughput and lower latency, memory usage, and energy consumption than stop-the-world collection.

Our work focuses more broadly on all VM services and in the context of AMP hardware, which is general purpose.

### 2.3 Summary

This chapter discussed how the prior work addresses the AMP architectures hardware complexity, as well as the overheads for managed software. In the following chapters, we will explain how to bring the two tracks together to hide each other's disadvantages and exploit their advantages. To more deeply understand the interaction of hardware and software in a modern setting, we start with measurements. We perform a detailed analysis of the power, energy and performance characteristics of managed as well as native software on a range of hardware features.

## Power and Performance Characteristics for Language and Hardware

To improve the efficiency of hardware supporting managed software and managed software utilising available hardware, we need to comprehensively understand the power, performance and energy characteristics of current hardware features and software. This chapter reports and analyzes measured chip power and performance on five process technology generations covering six hardware features (chip multiprocessors, simultaneous multithreading, clock scaling, die shrink, microarchitecture and turbo boost) executing a diverse set of benchmarks.

This chapter is structured as follows. Section 3.2 describes the hardware, workload, measurements, and software configuration. Section 3.3 examines the energy tradeoffs made by each processor over time and conducts a Pareto energy efficiency analysis to find out which hardware settings are more efficient for managed and native benchmarks. Section 3.4 explores the energy impact of hardware features.

This chapter describes work published in the paper "Looking Back on the Language and Hardware Revolutions: Measured Power, Performance, and Scaling" [Esmaeilzadeh, Cao, Yang, Blackburn, and McKinley, 2011b], in the paper "What is Happening to Power, Performance, and Software?" [Esmaeilzadeh, Cao, Yang, Blackburn, and McKinley, 2012a], and in the paper "Looking Back and Looking Forward: Power, Performance, and Upheaval" [Esmaeilzadeh, Cao, Yang, Blackburn, and McKinley, 2012b]. All the data are published in the ACM Digital Library as a companion to this paper [Esmaeilzadeh, Cao, Yang, Blackburn, and McKinley, 2011c]. In this collaboration, I was primarily responsible for managed software and hardware feature analysis.

### 3.1 Introduction

Quantitative performance analysis is the foundation for computer system design and innovation. In their classic paper, Emer and Clark noted that "A lack of detailed timing information impairs efforts to improve performance" [Emer and Clark, 1984].

They pioneered the quantitative approach by characterizing instruction mix and cycles per instruction on timesharing workloads. They surprised expert reviewers by demonstrating a gap between the theoretical 1 MIPS peak of the VAX-11/780 and the 0.5 MIPS it delivered on real workloads [Emer and Clark, 1998]. Industry and academic researchers in software and hardware all use and extend this principled performance analysis methodology. Our research applies this quantitative approach to measured power. This work is timely because the past decade heralded the era of power and energy constrained hardware design. A lack of detailed energy measurements is impairing efforts to reduce energy consumption on modern workloads.

Using controlled hardware configurations, we explore the energy impact of hardware features and workloads. We perform historical and Pareto analyses that identify the most power and performance efficient designs in our architecture configuration space. Our data quantifies a large number of workload and hardware trends with precision and depth, some known and many previously unreported. Our diverse findings include the following: (a) native sequential workloads do not approximate managed workloads or even native parallel workloads; (b) diverse application power profiles suggest that future applications and system software will need to participate in power optimization and management; and (c) software and hardware researchers need access to real measurements to optimize for power and energy.

### 3.2 Methodology

This section describes our benchmarks, compilers, Java Virtual Machines, operating system, hardware, and performance measurement methodologies.

#### 3.2.1 Benchmarks

The following methodological choices in part prescribe our choice of benchmarks. (1) *Individual benchmark performance and average power:* We measure execution time and average power of individual benchmarks in isolation and aggregate them by workload type. While multi-programmed workload measurements, such as SPECrate can be valuable, the methodological and analysis challenges they raise are beyond the scope of this thesis. (2) *Language and parallelism:* We systematically explore native / managed, and scalable / non-scalable workloads. We create four benchmark groups in the cross product and weight each group equally.

**Native Non-scalable**: C, C++ and Fortran single threaded benchmarks from SPEC CPU2006.

Native Scalable: Multithreaded C and C++ benchmarks from PARSEC.

**Java Non-scalable**: Single and multithreaded benchmarks that do not scale well from SPECjvm, DaCapo 06-10-MR2, DaCapo 9.12, and pjbb2005 [Blackburn et al., 2006].

**Java Scalable**: Multithreaded benchmarks from DaCapo 9.12, selected because their performance scales similarly to Native Scalable on the i7 (45).

| Grp Src               | Name          | Time (s)   | Description                                                                      |

|-----------------------|---------------|------------|----------------------------------------------------------------------------------|

|                       | perlbench     | 1037       | Perl programming language                                                        |

|                       | bzip2         | 1563       | bzip2 Compression                                                                |

|                       | gcc           | 851        | C optimizing compiler                                                            |

|                       | mcf           | 894        | Combinatorial opt/singledepot vehicle scheduling                                 |

|                       | gobmk         | 1113       | Al: Go game                                                                      |

|                       | hmmer         | 1024       | Search a gene sequence database                                                  |

| SI                    | sjeng         | 1315       | Al: tree search & pattern recognition                                            |

|                       | libquantum    | 629        | Physics / Quantum Computing                                                      |

|                       | h264ref       | 1533       | H.264/AVC video compression                                                      |

|                       | omnetpp       | 905        | Ethernet network simulation based on OMNeT + +                                   |

|                       | astar         | 1154       | Portable 2D path-finding library                                                 |

| Native Non-scalable   | xalancbmk     | 787        | XSLT processor for transforming XML                                              |

| calg                  | gamess        | 3505       | Quantum chemical computations                                                    |

| J-S                   | milc          | 640        | Physics/quantum chromodynamics (QCD)                                             |

| ō                     | zeusmp        | 1541       | Physics/Magnetohydrodynamics based on ZEUS-MP                                    |

| e e                   | gromacs       | 983        | Molecular dynamics simulation                                                    |