### COMP2300-COMP6300-ENGN2219 Computer Organization & Program Execution

#### Convener: Shoaib Akram shoaib.akram@anu.edu.au

Australian National University

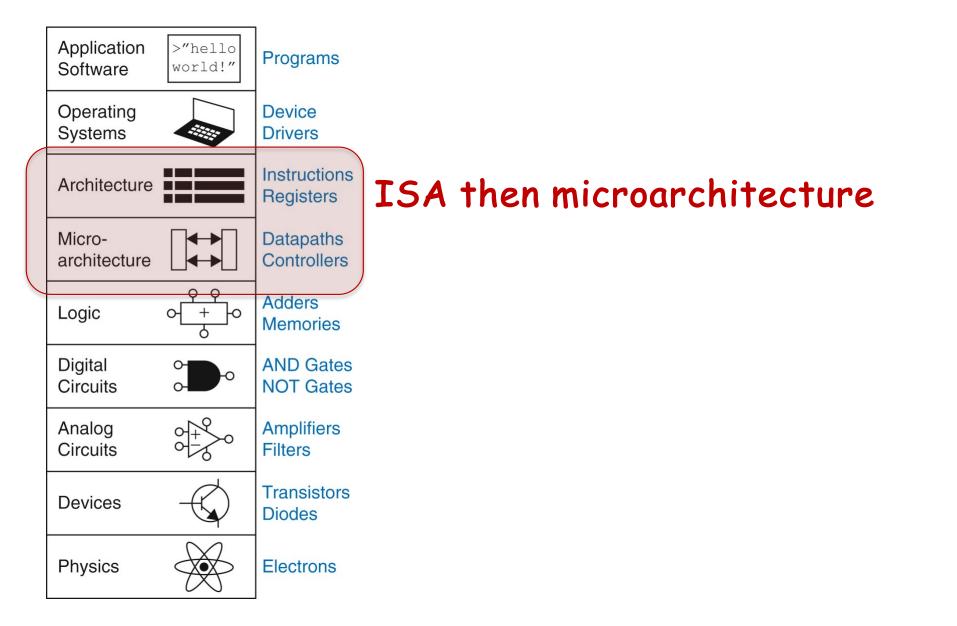

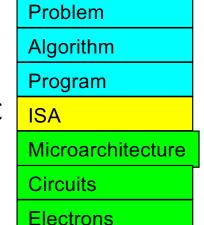

#### **Our Status**

- We are done with digital logic fundamentals that we need to understand and build a CPU

- We are now (+ next week) at

- Architecture layer

- Then

- Microarchitecture layer

#### Admin

- Quiz #1 has been marked

- We will take the best two of four quizzes

- Marking of the checkpoint is underway

- Assignment 1 will be released this week

- Some % of assignment 1 grade comes from work you are doing in Labs 4 6

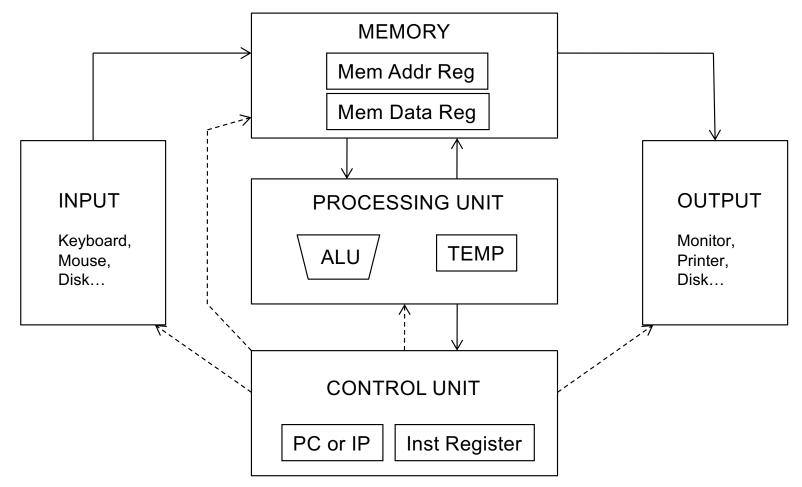

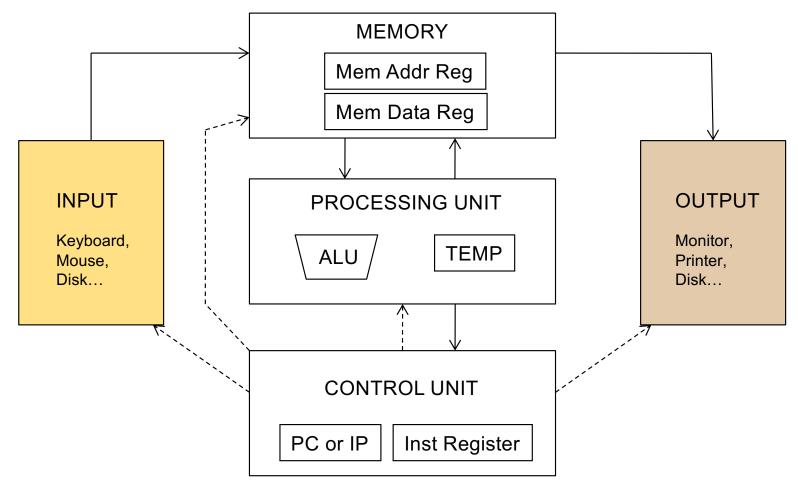

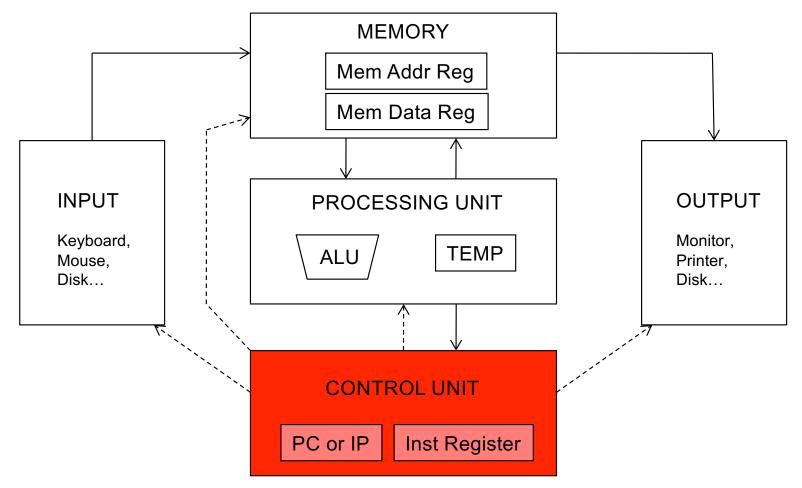

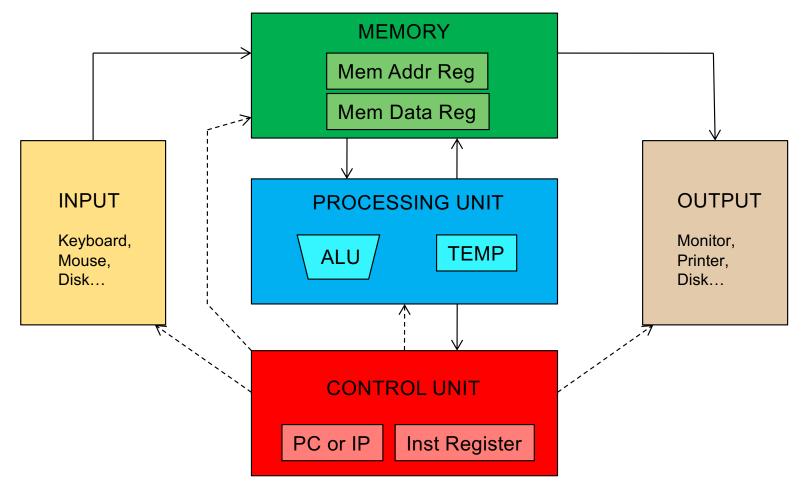

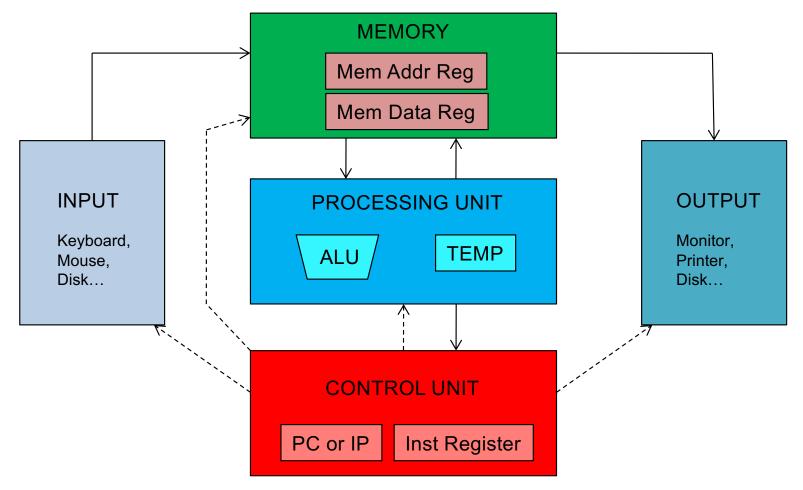

#### Von Neumann Model

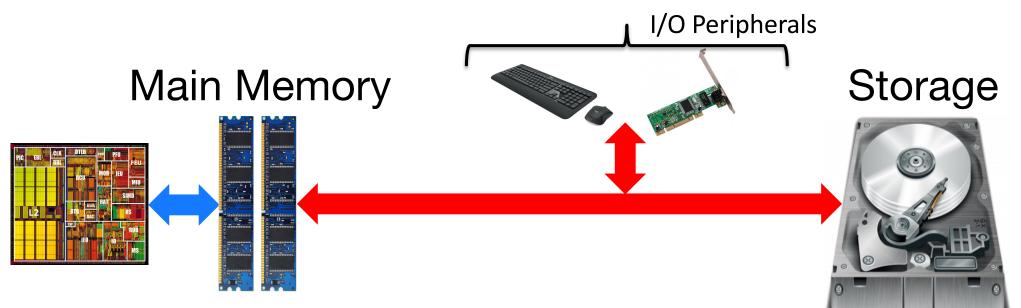

#### **Recall: A Computer System**

- Key resources: CPU, memory, and Input/Output (I/O) devices

- CPU (microprocessor) does the actual processing (computation)

- Memory stores temporary data and forms a hierarchy (registers, SRAM, DRAM, ...)

- Some fast (small capacity) memory called register file is close to the CPU and rest is far

- Storage disk is an I/O device (much slower than memory, stores persistent data)

- Memory is volatile, while disk is non-volatile (data is retained after a shutdown)

- Other peripherals such as keyboard and network card are accessories to processing

#### **Another View: What is a Computer?**

Basic computer model proposed in the 1940s

We will cover all three components

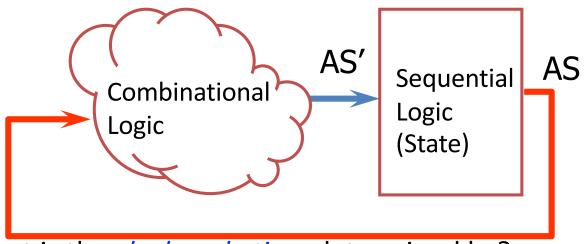

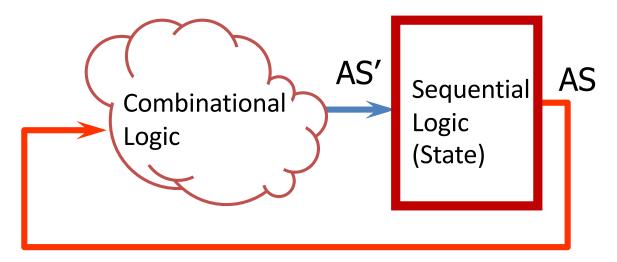

### **Building up a Basic Computer Model**

- In past lectures, we learned how to design

- Combinational logic structures

- Sequential logic structures

- With logic structures, we can build

- Execution units

- Decision units

- Memory/storage units

- Communication units

- All are basic elements of a computer

- We will raise our abstraction level today

- Use logic structures to construct a basic computer model

|                                                         | Problem   |  |  |

|---------------------------------------------------------|-----------|--|--|

| Algorithm                                               |           |  |  |

| Program in C/Jav<br>Runtime System<br>(Operating system |           |  |  |

|                                                         |           |  |  |

| Microarchitecture                                       |           |  |  |

|                                                         | Logic     |  |  |

|                                                         | Devices   |  |  |

|                                                         | Electrons |  |  |

|                                                         |           |  |  |

# **Building up a Basic Computer Model**

- ISA: Specification of the instructions computer can perform

- An interface between the programs and hardware

- Programmer needs to know ISA to be able to convey his wishes (instructions) to the hardware

- Hardware builder (computer architect) needs to know the ISA to be able to build and organize circuits to carry out the instructions

- Microarchitecture: Circuit implementation of the specification

- An important aspect to ponder: Not every implementation detail is relevant to the programmer!

- Just enough to be able to program the computer (as we will see)

| Problem                              |  |

|--------------------------------------|--|

| Algorithm                            |  |

| Program in C/Java                    |  |

| Runtime System<br>(Operating system) |  |

| ISA (Architecture)                   |  |

| Microarchitecture                    |  |

| Logic                                |  |

| Devices                              |  |

| Electrons                            |  |

### ISA vs. Microarchitecture

- What is part of ISA vs. Uarch?

- Gas pedal: interface for "acceleration"

- Internals of the engine: implement "acceleration"

- Aspects of ISA

- The different instructions and their binary codes

- Semantics (meaning) of each instruction

- Word size, number of registers, memory addressability

- Aspects of implementation

- Ripple-carry vs. carry-lookahead adder

- Mux or tristate buffers

- Canonical SOP or minimal Boolean expression for implementation

- NAND gates only vs. AND/OR/NOT combination

#### ISA vs. Microarchitecture

- One ISA can have many microarchitectures

- One microarchitecture per student, but the QuAC ISA is the same on the course webpage

- ISA is usually a one-time effort with incremental changes to enable new applications

- Only a few ISAs in the world but many microarchitectures

- Microarchitecture changes faster than ISA

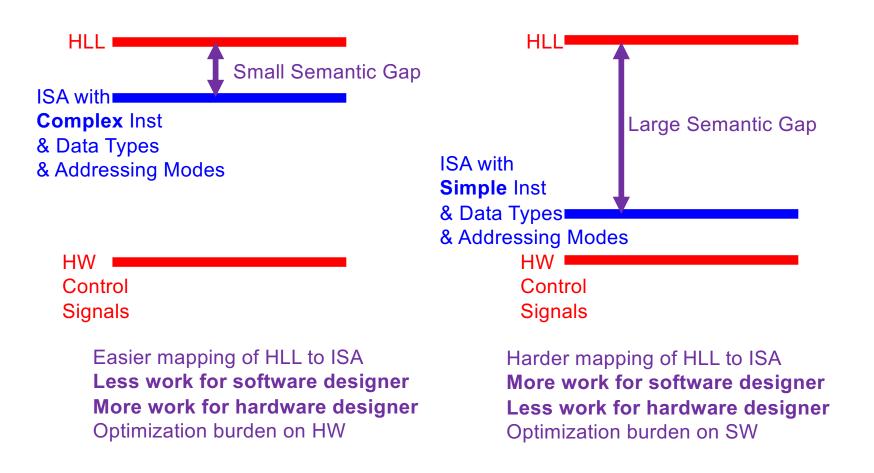

- Key insight: ISA can enable simple vs. complex logic gate circuitry at the microarchitecture level (more in coming weeks ....

#### **ISA: Another View**

- Most people don't write programs in the computer's own machine language (lowest level)

- They prefer high-level languages such as C++, Java, or Python

- A compiler translates C++ or Java code into the computer's machine language

- ISA specifies everything in the computer that a compiler writer who wishes to translate programs from C++/Java to machine language need to know

#### ISAs are a Good Bedtime Reading!

Combined Volume Set of Intel® 64 and IA-32 Architectures Software Developer's Manuals

| Document                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RESOURCES                       |                                                                                                                                                                                                                                            |                 |                                      |                                          |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------|------------------------------------------|

| Intel® 64 and IA-32 Architectures                          | This document contains the following:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Assembler Guide                 |                                                                                                                                                                                                                                            |                 |                                      |                                          |

| Software Developer's Manual                                | This document contains the following.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Software setup                  | QuAC ISA V0.2                                                                                                                                                                                                                              |                 |                                      | VU.Z                                     |

| Combined Volumes: 1, 2A, 2B, 2C, 2D, 3A, 3B, 3C, 3D, and 4 | Volume 1: Describes the architecture and programming environment of processors supporting IA-32 and Intel® 64 architectures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Writing a design document       | This document is the definitive source of the $QuAC^1$ ins                                                                                                                                                                                 |                 | source of the $QuAC^{1}$ instruction |                                          |

|                                                            | Volume 2: includes the full instruction set reference. A-Z. Describes the format of the instruction and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | QUACISA                         | set that we will be implementing in this course. If another source                                                                                                                                                                         |                 |                                      |                                          |

|                                                            | volume 2: includes the full instruction set reference, A-2. Describes the format of the instruction and<br>provides reference pages for instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | QuAC Extensions                 | contradicts this document, this takes precedance.                                                                                                                                                                                          |                 |                                      |                                          |

|                                                            | Volume 3: Includes the full system programming guide, parts 1, 2, 3, and 4. Describes the operating-system support environment of Intel® 64 and IA-32 architectures, including memory management, protection, task management, interrupt and exception handling, multi-processor support, thermal and power management features, debugging, performance monitoring, system management mode, virtual machine extensions (VMX) instructions, Intel® Virtualization Technology (Intel® VT), and Intel® Software Guard Extensions (Intel® SGX). NOTE: Performance monitoring events can be found here: https://perfmon-events.intel.com/ | QuAC Instruction<br>Description | Memory                                                                                                                                                                                                                                     |                 |                                      |                                          |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RELATED SITES                   | <ul> <li>Minimum addressable unit is 16-bit words</li> <li>16-bit addressed</li> <li>Total addressable memory is 128 kb (64k words)</li> <li>Registers</li> <li>All registers start initalised to 0x0000, and are 16-bits wide.</li> </ul> |                 |                                      |                                          |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Piazza                          |                                                                                                                                                                                                                                            |                 |                                      |                                          |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Streams                         |                                                                                                                                                                                                                                            |                 |                                      |                                          |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Wattle                          |                                                                                                                                                                                                                                            |                 |                                      |                                          |

|                                                            | architectures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SoCo Homepage                   |                                                                                                                                                                                                                                            |                 |                                      |                                          |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                 | All reg                                                                                                                                                                                                                                    | isters start ir | nitalised to                         | dx0000, and are 16-bits wide.            |

| Itel® 64 and IA-32 Architectures                           | Describes bug fixes made to the Intel® 64 and IA-32 architectures software developer's manual between<br>versions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 | Code                                                                                                                                                                                                                                       | Mnemonic        | Meaning                              | Behaviour                                |

| Documentation Changes                                      | NOTE: This change document applies to all Intel® 64 and IA-32 architectures software developer's manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 | 000                                                                                                                                                                                                                                        | rz              | Zero<br>Register                     | Always read zero, writes have no effect. |

|                                                            | sets (combined volume set, 4 volume set, and 10 volume set).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                 | 001                                                                                                                                                                                                                                        | r1              | Register 1                           | General purpose register.                |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                 |                                                                                                                                                                                                                                            |                 |                                      |                                          |

#### TABLE OF CONTENTS

QuAC ISA V0.2

Memory

Registers

t we will be implementing in this course. If another source Instruction Encoding dicts this document, this takes precedance.

> Register Operands Format (R-Mode)

Immediate Format

(I-Mode)

Definitions

All Modes

R-Mode only

I-Mode Only

Hardware Instructions Pseudo-Instructions

Flag Register **Condition Codes**

| Code | Mnemonic   | Meaning          | Behaviour                                                                                                                                |

|------|------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 000  | rz         | Zero<br>Register | Always read zero, writes have no effect.                                                                                                 |

| 001  | <b>r</b> 1 | Register 1       | General purpose register.                                                                                                                |

| 010  | r2         | Register 2       | General purpose register.                                                                                                                |

| 011  | r3         | Register 3       | General purpose register.                                                                                                                |

| 100  | r4         | Register 4       | General purpose register.                                                                                                                |

| 101  | fl         | Flag<br>register | Stores the flags from ALU<br>whenever an ALU instruction is<br>executed. Any operation can<br>read this register. Write is<br>undefined. |

### ISAs You Will Encounter @ ANU

- QuAC

- An ISA for educational purposes developed at ANU

- Mainly covered in tutorials and required for assignment 1

- MIPS

- Pioneering RISC ISA developed by John Hennessy at MIPS computer systems

- Microprocessors without Interlocked Pipelined Stages

- Briefly covered in today's lecture for breadth

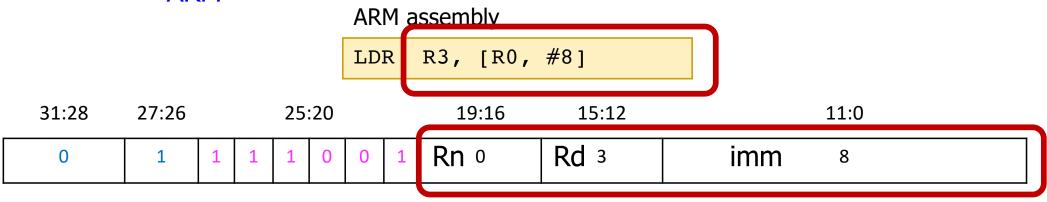

- ARM

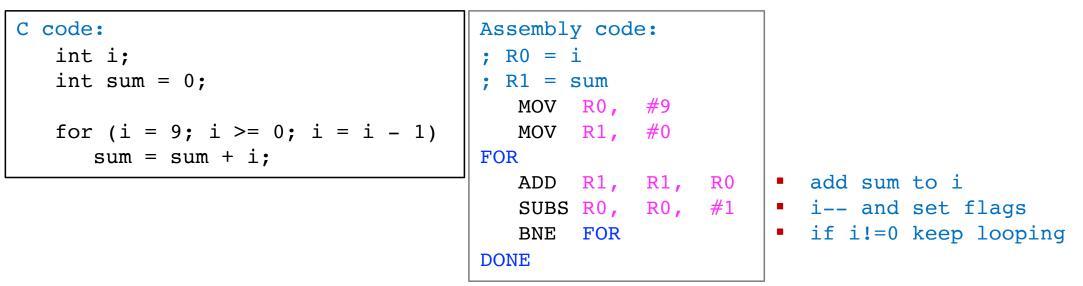

- A popular **RISC** ISA developed by Arm Ltd.

- Advanced RISC Machines

- De facto choice for portable hand-held devices

- Covered extensively in lectures and required for assignment 2

- LC-3

- Little Computer 3 is an educational ISA developed by Yale N. Patt at UT-Austin

- Briefly covered in today's lecture for breadth

- x86-64

- A CISC ISA developed by Intel Corporation

- Most influential ISA in the world and de facto choice for high-performance computing

- Covered extensively in COMP2310

Ex-President of Stanford University Chairman of Alphabet Founder of MIPS Technologies Turing Award Winner

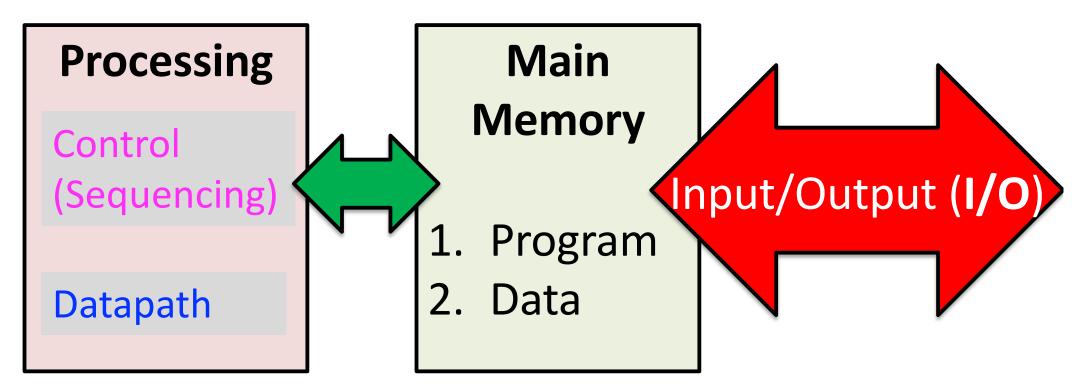

### What is a Computer?

- To get a task done by a (general-purpose) computer, we need

- A computer program

- That specifies what the computer must do

- The computer itself

- To carry out the specified task

- Program: A set of instructions

- Each instruction specifies a well-defined piece of work for the computer to carry out

- Instruction: the smallest piece of specified work in a program

- Instruction set: All possible instructions that a computer is designed to be able to carry out

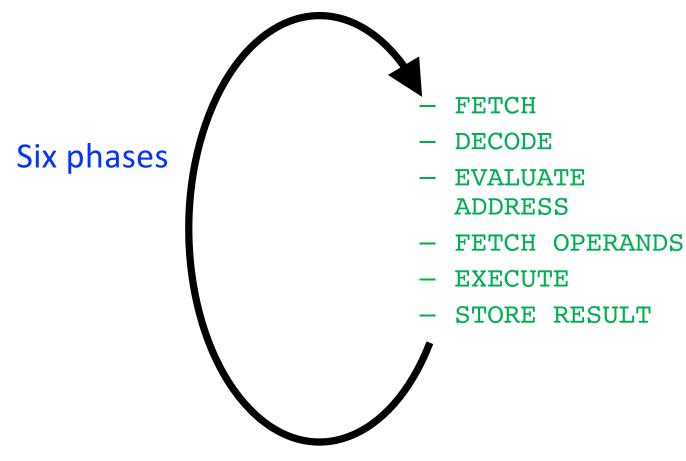

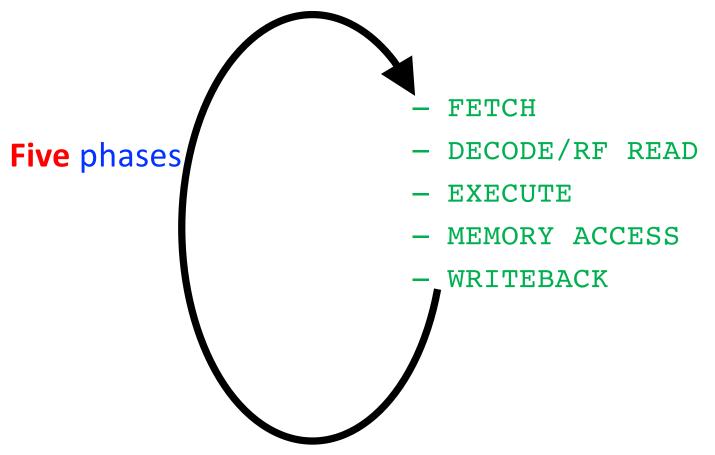

- In order to build a computer, we need an execution model for processing computer programs

- John von Neumann proposed a fundamental model in 1946

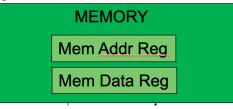

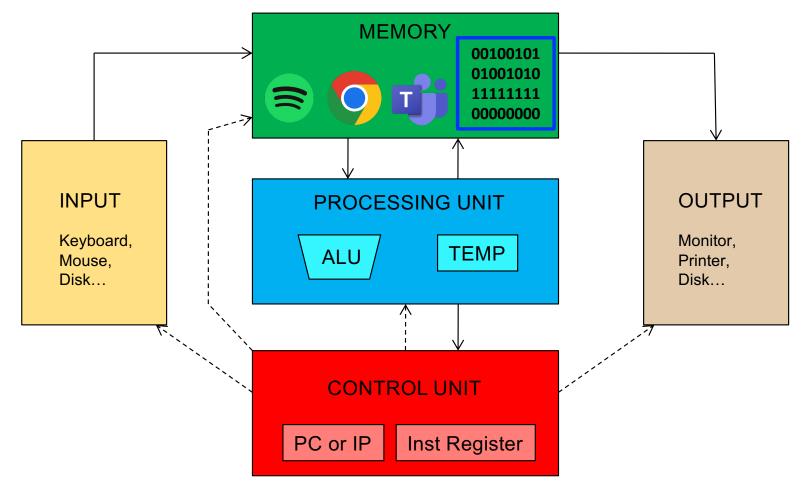

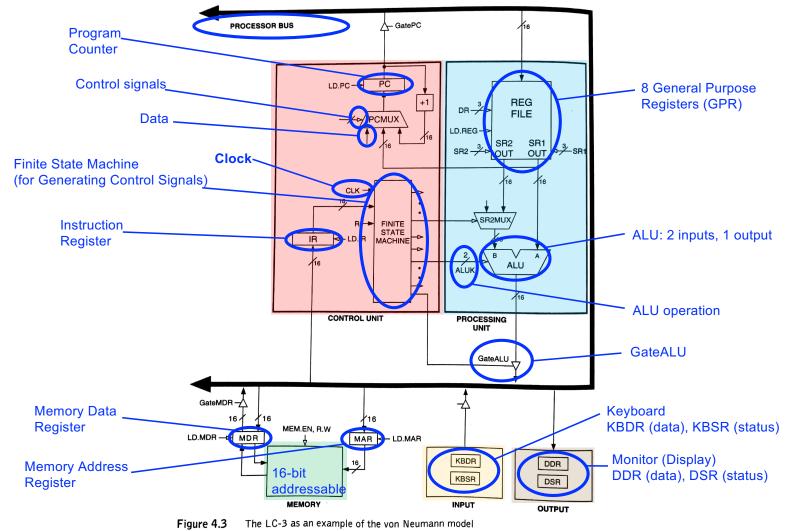

- The von Neumann Model consists of 5 components

- Memory (stores the program and data)

- Processing unit

- Input

- Output

- Control unit (controls the order in which instructions are carried out)

All general-purpose computers today use the von Neumann model

Burks, Goldstein, von Neumann, "Preliminary discussion of the logical design of an electronic computing instrument," 1946.

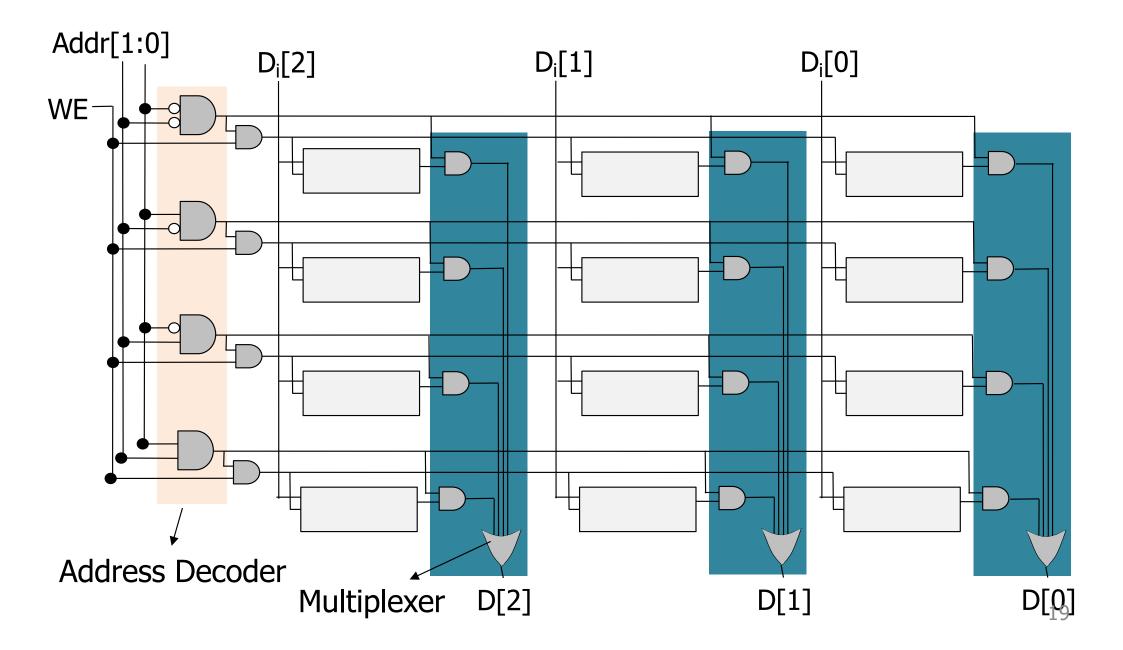

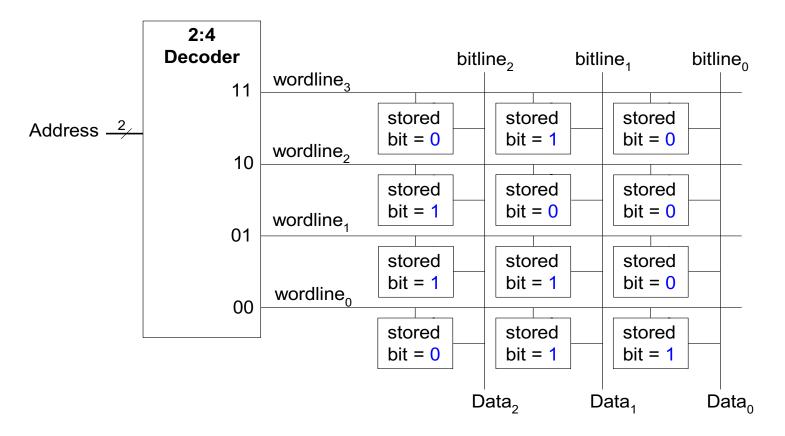

# Recall: A Memory Array (4 locations X 3 bits)

### **Recall: Memory Array Organization**

- Decoder drives the wordline HIGH based on the address

- Data on the selected row appears on the bitlines

20

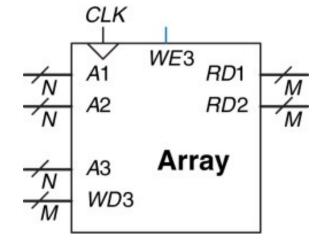

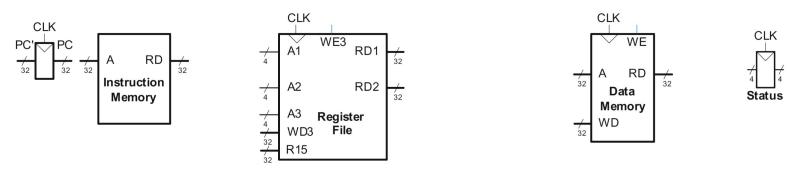

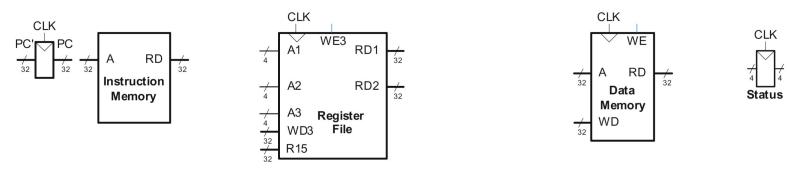

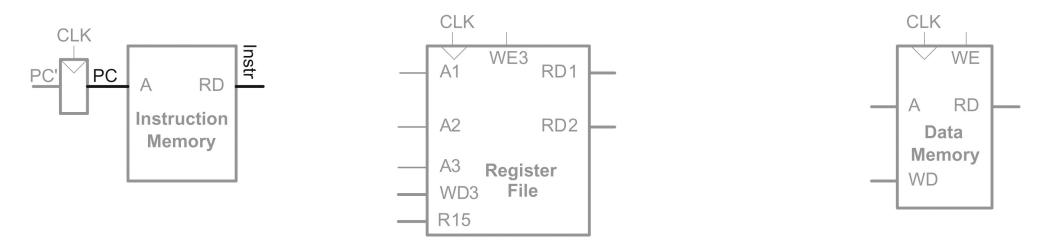

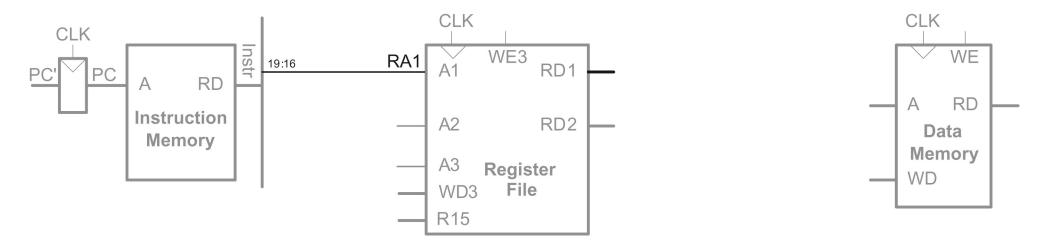

#### **Recall: Memory Ports**

- Each memory port gives read or write access to one memory address

- Multiported memories can access multiple addresses simultaneously

- Example of three-ported memory

- Port 1 reads the data from address A1 onto the read data output RD1

- Port 2 reads the data from address A2 onto the read data output RD2

- Port 3 writes the data from the write data input WD3 into address A3 on the rising clock edge if WE3 is TRUE

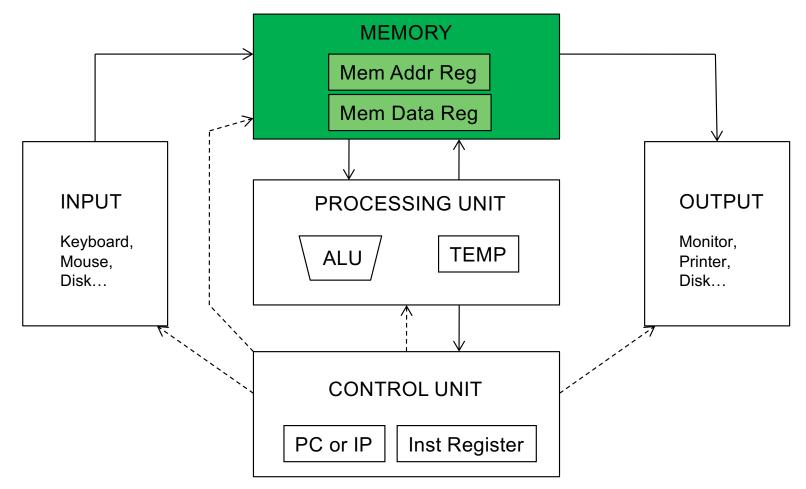

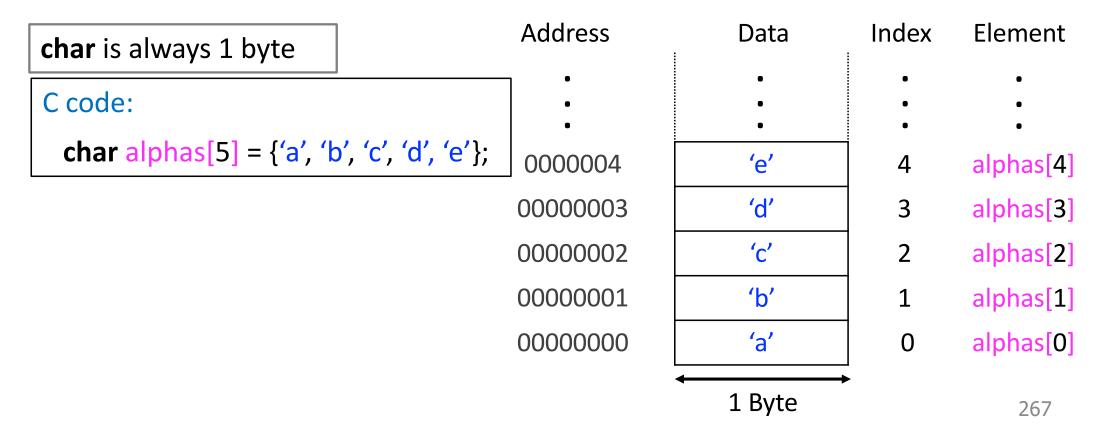

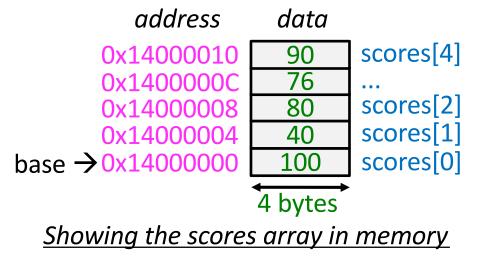

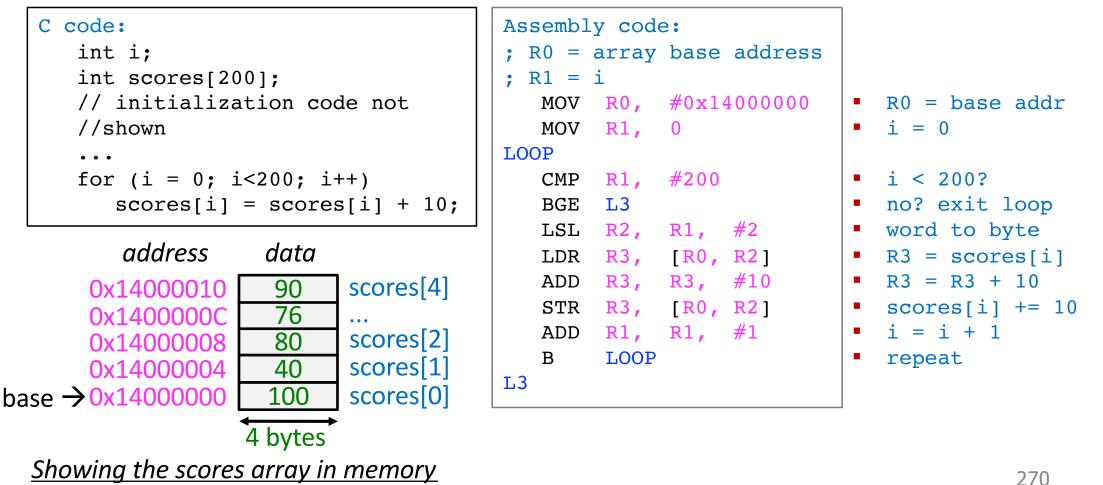

#### Memory

- Memory stores

- Programs

- Data

- Memory contains bits

- Bits are logically grouped into bytes (8 bits) and words (e.g., 8, 16, 32 bits)

- Address space: Total number of uniquely identifiable locations

- In MIPS, the address space is 2<sup>32</sup>

- 32-bit addresses

- In ARM, the address space is 2<sup>32</sup>

- 32-bit addresses

- In x86-64, the address space is (up to) 2<sup>48</sup>

- 48-bit addresses

- Addressability: How many bits are stored in each location (address)

- E.g., 8-bit addressable (or byte-addressable)

- E.g., word-addressable

- A given instruction can operate on a byte or a word

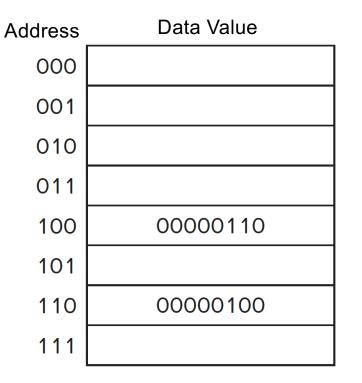

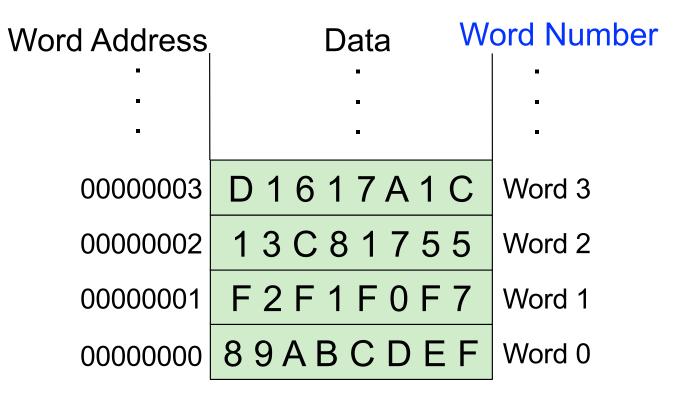

#### A Simple Example

- A representation of memory with 8 locations

- Each location contains 8 bits (one byte)

- Byte addressable memory with an address space of 8

- Value 6 is stored in address 4 & value 4 is stored in address 6

#### **Question:**

How can we make same-size memory bit addressable?

#### Answer:

64 locations Each location stores 1 bit

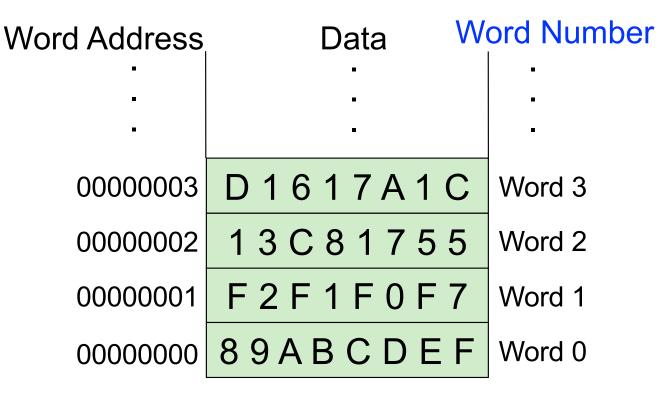

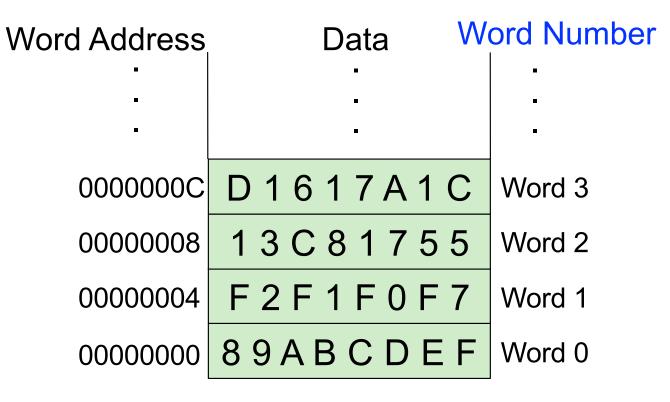

#### Word-Addressable Memory

- Each data word has a unique address

- In MIPS, a unique address for each 32-bit data word (not word-addressable)

- In QuAC, a unique address for each 16-bit data word (word addressable)

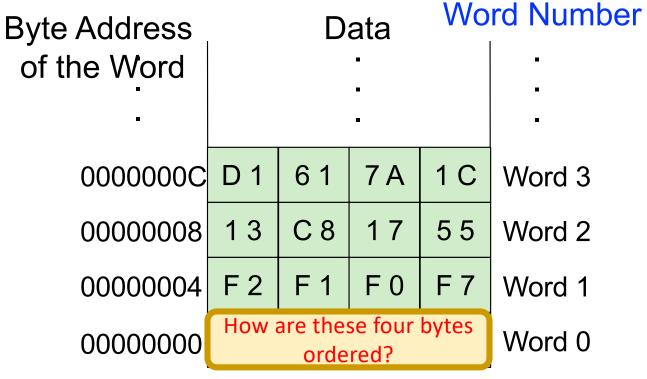

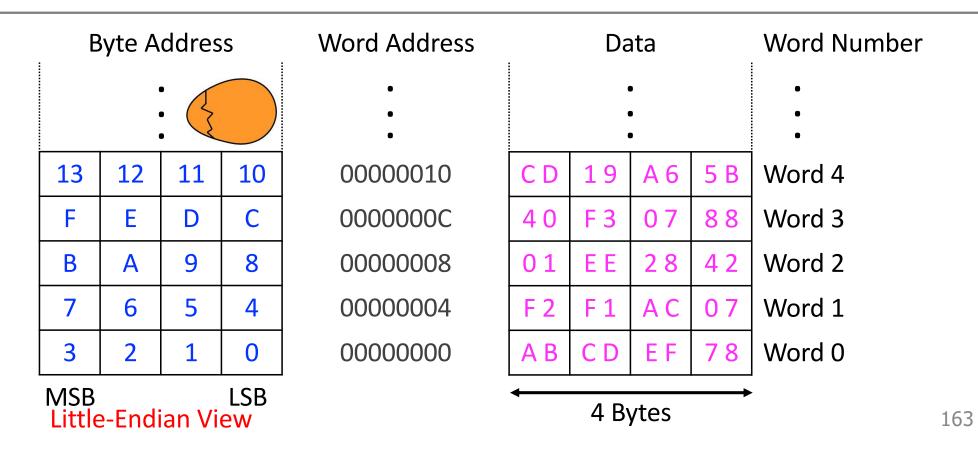

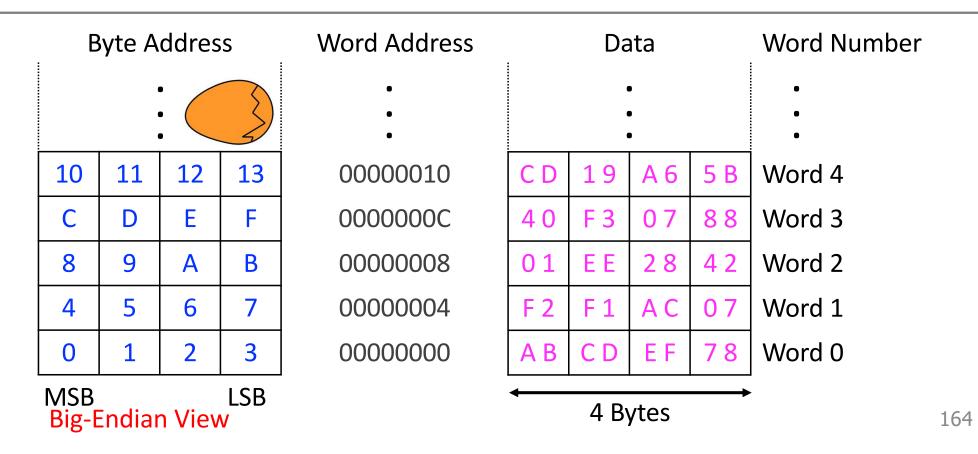

#### **Byte-Addressable Memory**

- Each byte has a unique address

- MIPS is actually byte-addressable

- ARM is also byte-addressable

Which of the four bytes is most vs. least significant?

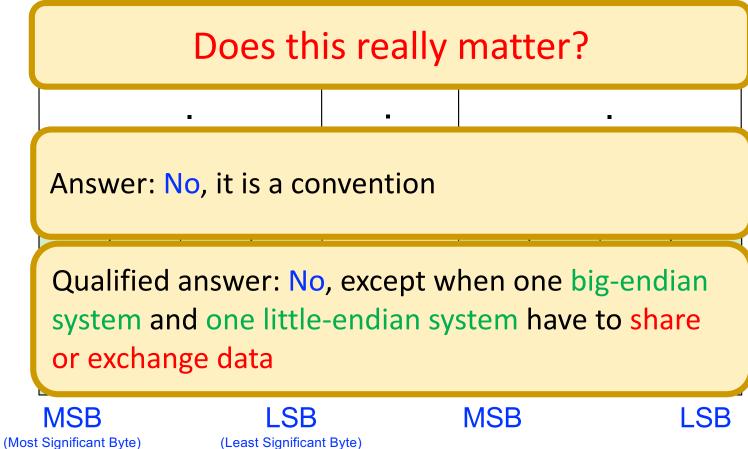

### Big Endian vs. Little Endian

- Jonathan Swift's Gulliver's Travels

- Big Endians broke their eggs on the big end of the egg

- Little Endians broke their eggs on the little end of the egg

BIG ENDIAN - The way people always broke their eggs in the Lilliput land

LITTLE ENDIAN - The way the king then ordered the people to break their eggs

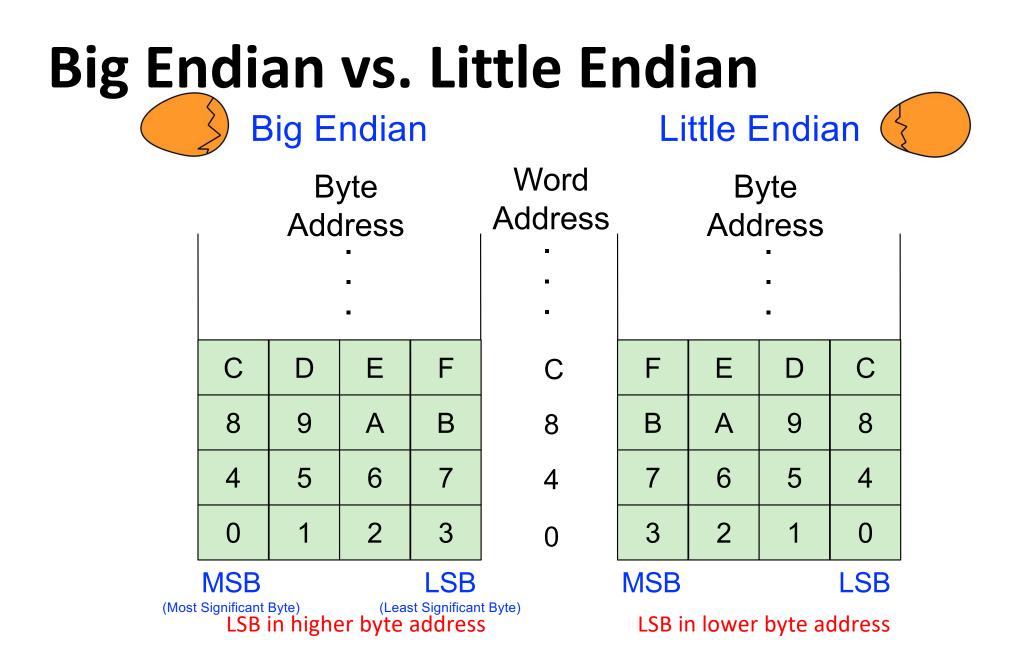

### Big Endian vs. Little Endian

- 0x01234567

- Memory addresses start at 0x100

Little Endian

### Big Endian vs. Little Endian

#### Big Endian

LSB in higher byte address

Little Endian

LSB in lower byte address

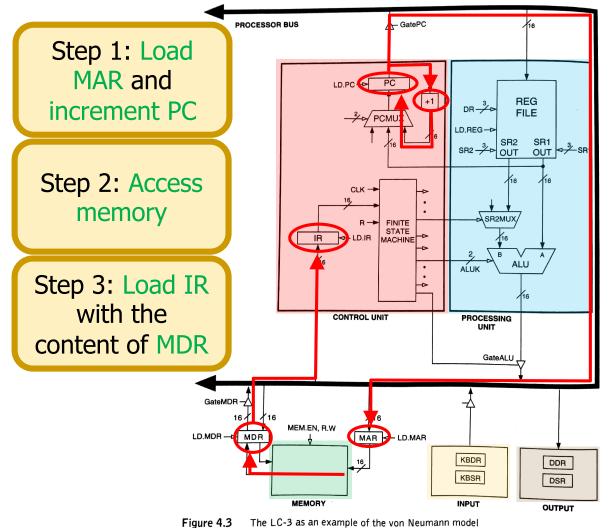

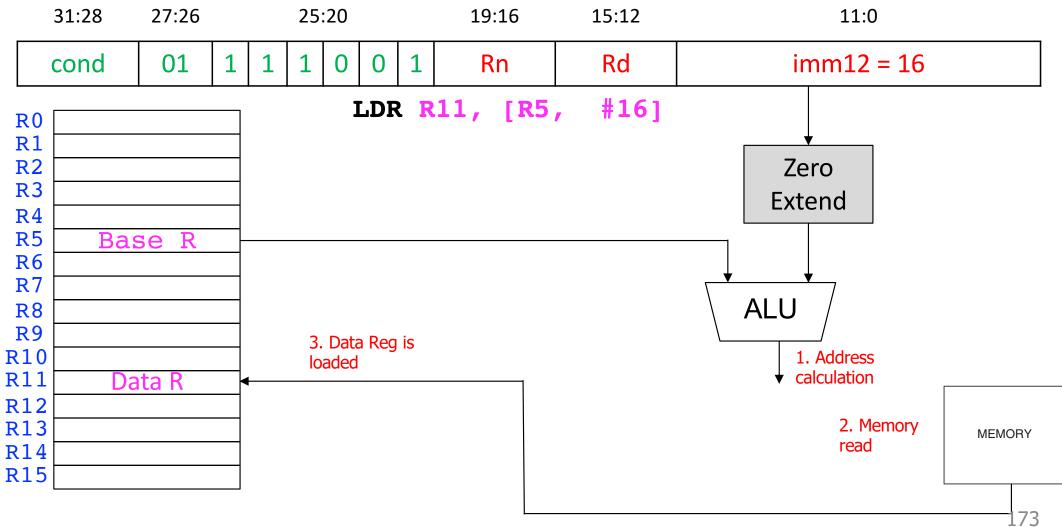

### Accessing Memory: MAR and MDR

- There are two ways of accessing memory

- Reading or loading data from a memory location

- Writing or storing data to a memory location

- Two registers are usually used to access memory

- Memory Address Register (MAR)

- Memory Data Register (MDR)

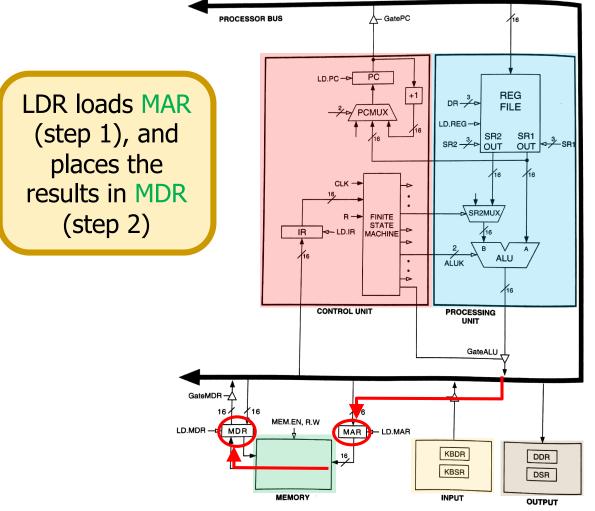

- To read

- Step 1: Load the MAR with the address we wish to read from

- Step 2: Data in the corresponding location gets placed in MDR

- To write

- Step 1: Load the MAR with the address and the MDR with the data we wish to write

- Step 2: Activate Write Enable signal → value in MDR is written to address specified by MAR

#### Learn to Distinguish Address from Data

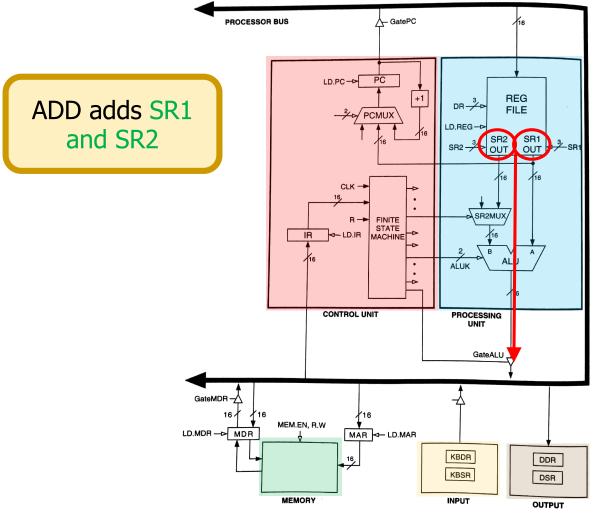

### **Processing Unit**

- Performs the actual computation(s)

- The processing unit can consist of many functional units

- We start with a simple Arithmetic and Logic Unit (ALU), which executes computation and logic operations

- ARM: ADD, AND, NOT, SUB

- MIPS: add, sub, mult, and, nor, sll, slr, slt...

- The ALU processes quantities that are referred to as words

- Word length in ARMv4 is 32 bits (v8 is 64 bits)

- Word length in MIPS is 32 bits

- Word length in QuAC is 16 bits

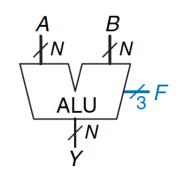

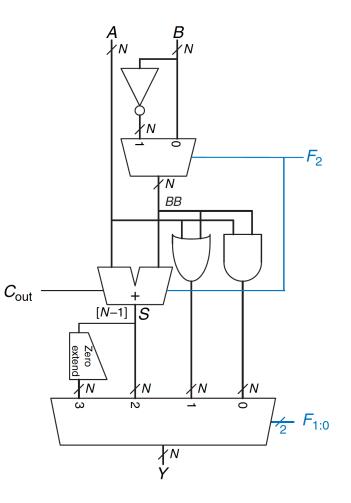

# Recall: Arithmetic & Logic Unit (ALU)

- Combines a variety of arithmetic and logical operations into a single unit (that performs only one function at a time)

- Usually denoted with this symbol:

Figure 5.14 ALU symbol

| <i>F</i> <sub>2:0</sub> | Function             |

|-------------------------|----------------------|

| 000                     | A AND B              |

| 001                     | A OR B               |

| 010                     | A + B                |

| 011                     | not used             |

| 100                     | A AND $\overline{B}$ |

| 101                     | A OR B               |

| 110                     | A – B                |

| 111                     | SLT                  |

#### Table 5.1 ALU operations

#### **Recall: Arithmetic & Logic Unit (ALU)**

| Table 5.1 ALU operations |                      |  |  |  |

|--------------------------|----------------------|--|--|--|

| F <sub>2:0</sub>         | Function             |  |  |  |

| 000                      | A AND B              |  |  |  |

| 001                      | A OR B               |  |  |  |

| 010                      | A + B                |  |  |  |

| 011                      | not used             |  |  |  |

| 100                      | A AND $\overline{B}$ |  |  |  |

| 101                      | A OR $\overline{B}$  |  |  |  |

| 110                      | А – В                |  |  |  |

| 111                      | SLT                  |  |  |  |

|                          |                      |  |  |  |

Table 5.1 ALL operations

35

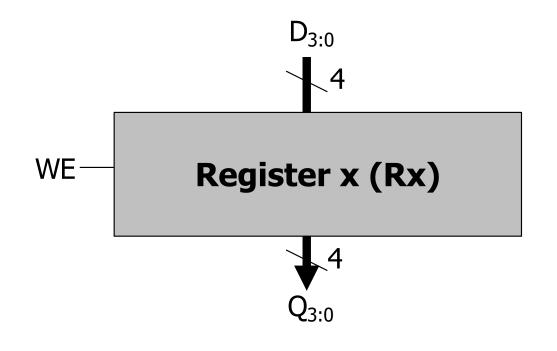

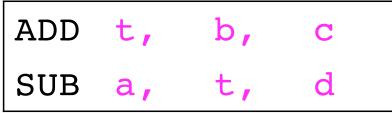

## **Processing Unit: Fast Temporary Storage**

- It is almost always the case that a computer provides a small amount of storage very close to ALU

- Purpose: to store temporary values and quickly access them later

- E.g., to calculate ((A+B)\*C)/D, the intermediate result of A+B can be stored in temporary storage

- Why? It is too slow to store each ALU result in memory & then retrieve it again for future use

- A memory access is much slower than an addition, multiplication or division

- Ditto for the intermediate result of ((A+B)\*C)

- This temporary storage is usually a set of registers

- Called Register File

## **Registers: Fast Temporary Storage**

**PROCESSING UNIT**

ALU

TEMP

- Memory is large but slow

- Registers in the Processing Unit

- Ensure fast access to values to be processed in the ALU

- Typically one register contains one word (same as word length)

- Register Set or Register File

- Set of registers that can be manipulated by instructions

- ARM has 16 general purpose registers (GPRs)

- R0 to R15: 4-bit register number

- Register size = Word length = 32 bits

- MIPS has 32 general purpose registers

- More elaborate naming scheme: 5-bit register number (or Register ID)

- Register size = Word length = 32 bits

- QuAC has 8 general purpose registers (one undefined)

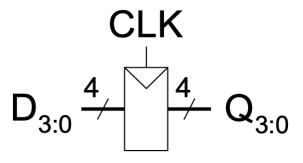

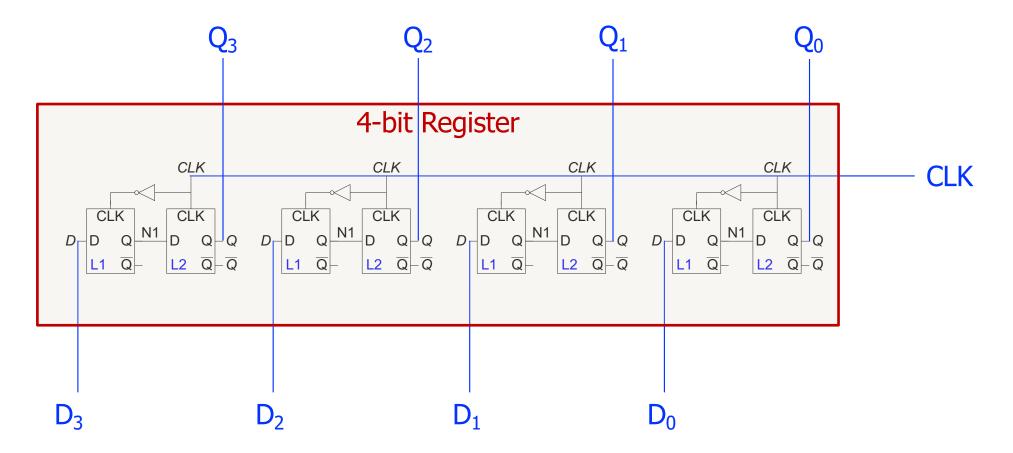

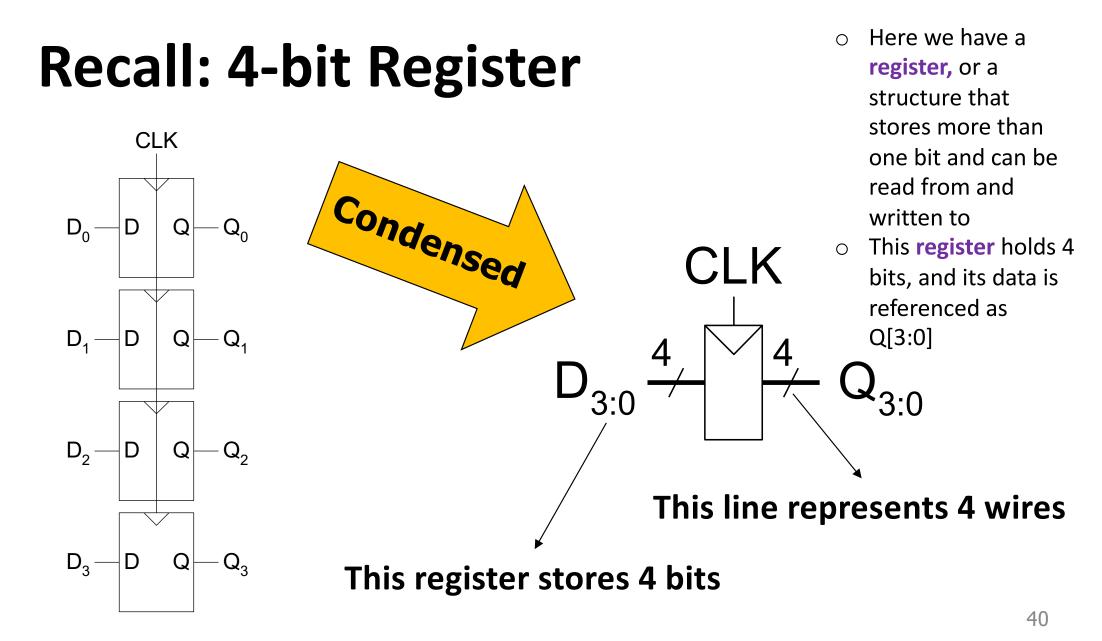

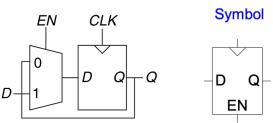

## **Recall: Register**

- How can we use flipflops to store more than one bit?

- Principle of modularity: Use more flipflops!

- A single CLK to simultaneously write to all flipflops

- Register: A structure that stores more than one bit of information and can be read from and written to

- This register holds 4 bits, and its data is referenced as Q[3:0]

## **Recall: 4-bit Register**

To build an N-bit register, use a bank of N flipflops with a shared CLK

## **More Realistic Register**

A single WE signal for all flip-flops for simultaneous writes

## How Registers are Addressed?

- Each ISA gives a set of general-purpose registers with special names

- So, an assembly programmer can use convenient names

- How they are translated into binary addresses is up to the implementation

- Let's see

## **MIPS Register File**

| Name      | Register Number | Usage                   |

|-----------|-----------------|-------------------------|

| \$0       | 0               | the constant value 0    |

| \$at      | 1               | assembler temporary     |

| \$v0-\$v1 | 2-3             | function return value   |

| \$a0-\$a3 | 4-7             | function arguments      |

| \$t0-\$t7 | 8-15            | temporary variables     |

| \$s0-\$s7 | 16-23           | saved variables         |

| \$t8-\$t9 | 24-25           | temporary variables     |

| \$k0-\$k1 | 26-27           | OS temporaries          |

| \$gp      | 28              | global pointer          |

| \$sp      | 29              | stack pointer           |

| \$fp      | 30              | frame pointer           |

| \$ra      | 31              | function return address |

## **ARM Register File**

#### Table 6.1 ARM register set

| Name     | Use                                          |

|----------|----------------------------------------------|

| R0       | Argument / return value / temporary variable |

| R1–R3    | Argument / temporary variables               |

| R4–R11   | Saved variables                              |

| R12      | Temporary variable                           |

| R13 (SP) | Stack Pointer                                |

| R14 (LR) | Link Register                                |

| R15 (PC) | Program Counter                              |

# LC-3 Register File (with Contents)

| Register 0 | (RO) | 000000000000000000000000000000000000000 |

|------------|------|-----------------------------------------|

| Register 1 | (R1) | 000000000000011                         |

| Register 2 | (R2) | 000000000000101                         |

| Register 3 | (R3) | 000000000000111                         |

| Register 4 | (R4) | 1111111111111110                        |

| Register 5 | (R5) | 1111111111111100                        |

| Register 6 | (R6) | 1111111111111010                        |

| Register 7 | (R7) | 1111111111111000                        |

## **QuAC Register File**

#### Registers

All registers start initalised to 0x0000, and are 16-bits wide.

| Code | Mnemonic   | Meaning         | Behaviour                                          |

|------|------------|-----------------|----------------------------------------------------|

| 000  | rz         | Zero Register   | Always reads as zero, even after being written to. |

| 001  | <b>r1</b>  | Register 1      | General purpose register.                          |

| 010  | r2         | Register 2      | General purpose register.                          |

| 011  | <b>r</b> 3 | Register 3      | General purpose register.                          |

| 100  | r4         | Register 4      | General purpose register.                          |

| 101  | fl         | Flag register   | See <u>Flags</u> .                                 |

| 110  | -          | Undefined       | Any operation with this register is undefined.     |

| 111  | рс         | Program Counter | See <u>Program Counter</u> .                       |

- rz, fl, and pc may also be described as r0, r5, and r7 respectively.

- An instruction is allowed to write to rz, however the next time an instruction reads rz it will still read as 0.

- r1, r2, r3, and r4 are the general purpose registers. You may write to them, and they will store that value. Reading from a general purpose register returns the last value written to them.

## The Von Neumann Model

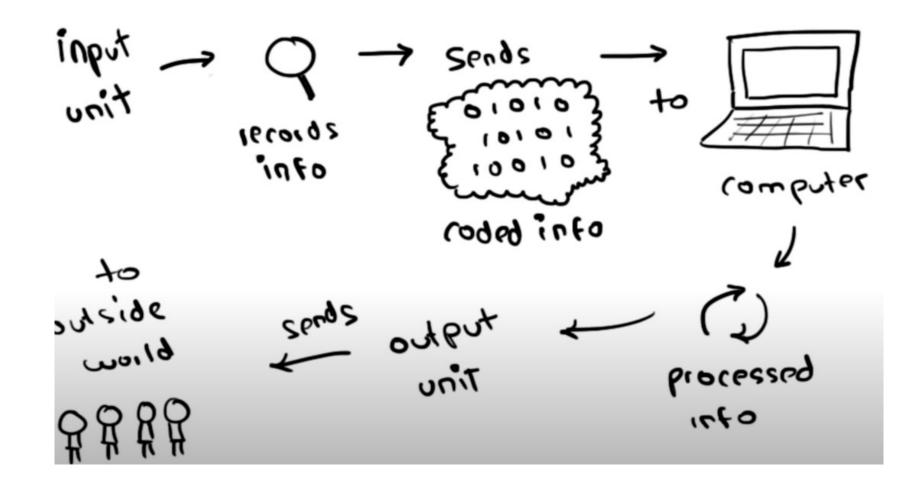

## Input and Output

- Enable information to get into and out of a computer

- Many devices can be used for input and output

- They are called peripherals

- Input

- Keyboard

- Mouse

- Scanner

- Disks

- Etc.

- Output

- Monitor

- Printer

- Disks

- Etc.

## Input and Output

# **Keyboard and Monitor**

- The simplest keyboard has two registers

- Keyboard data register (KBDR) for holding the ASCII code of keys struck

- Keyboard status register (KBSR) for maintaining status information about the keys struck

- The simplest monitor has two registers

- Display data register (DDR) for holding the ASCII code of something to be displayed on the screen

- Display status register (DSR) for maintaining associated status information

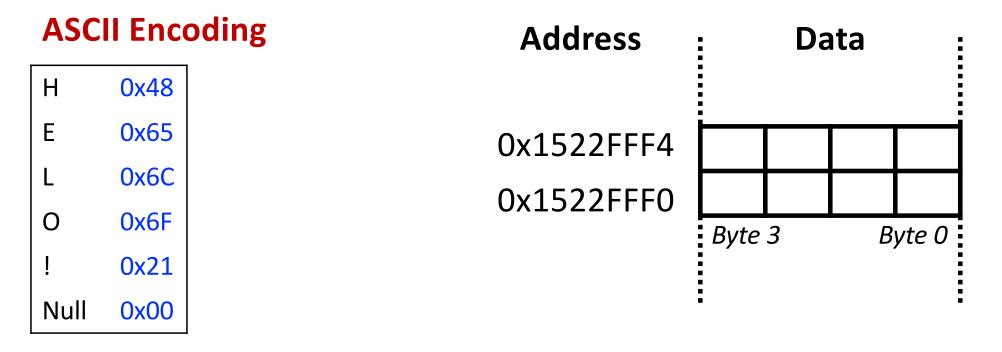

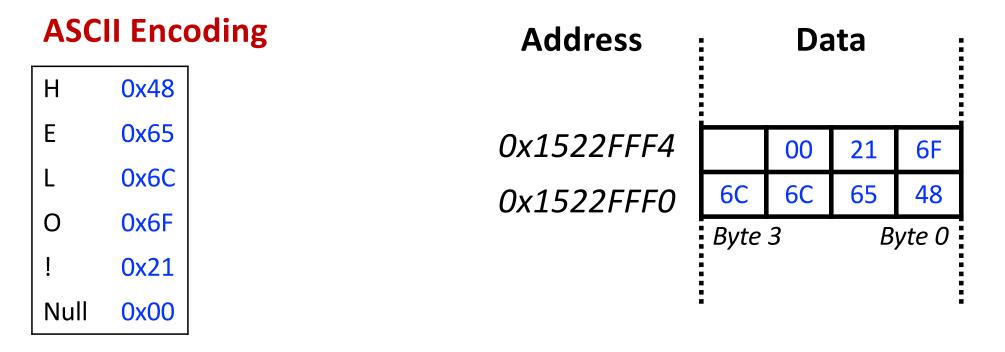

# **ASCII Encoding**

- ASCII stands for American Standard Code for Information Interchange

- It ranges from 0 to 255 in Decimal or 00 to FF in Hexadecimal

- All characters on an English keyboard can be represented using 8-bit codes

| Dec | Hex | Name              | Char | Ctrl-char | Dec | Hex | Char  | Dec | Hex | Char | Dec | Hex | Char |

|-----|-----|-------------------|------|-----------|-----|-----|-------|-----|-----|------|-----|-----|------|

| 0   | 0   | Null              | NUL  | CTRL-@    | 32  | 20  | Space | 64  | 40  | ۹    | 96  | 60  | +    |

| 1   | 1   | Start of heading  | SOH  | CTRL-A    | 33  | 21  | 1     | 65  | 41  | A    | 97  | 61  | а    |

| 2   | 2   | Start of text     | STX  | CTRL-B    | 34  | 22  |       | 66  | 42  | в    | 98  | 62  | b    |

| 3   | 3   | End of text       | ETX  | CTRL-C    | 35  | 23  | #     | 67  | 43  | С    | 99  | 63  | C    |

| 4   | 4   | End of xmit       | EOT  | CTRL-D    | 36  | 24  | \$    | 68  | 44  | D    | 100 | 64  | d    |

| 5   | 5   | Enquiry           | ENQ  | CTRL-E    | 37  | 25  | %     | 69  | 45  | E    | 101 | 65  | e    |

| 6   | 6   | Acknowledge       | ACK  | CTRL-F    | 38  | 26  | 8     | 70  | 46  | F    | 102 | 66  | f    |

| 7   | 7   | Bell              | BEL  | CTRL-G    | 39  | 27  | •     | 71  | 47  | G    | 103 | 67  | g    |

| 8   | 8   | B ackspace        | BS   | CTRL-H    | 40  | 28  | (     | 72  | 48  | н    | 104 | 68  | h    |

| 9   | 9   | Horizontal tab    | HT   | CTRL-I    | 41  | 29  | )     | 73  | 49  | 1    | 105 | 69  | i i  |

| 10  | 0A  | Line feed         | LF   | CTRL-J    | 42  | 2A  | •     | 74  | 4A  | 1    | 106 | 6A  | j    |

| 11  | 0B  | Vertical tab      | VT   | CTRL-K    | 43  | 28  | +     | 75  | 4B  | ĸ    | 107 | 6B  | k    |

| 12  | 0C  | Form feed         | FF   | CTRL-L    | 44  | 2C  |       | 76  | 4C  | L    | 108 | 6C  | 1    |

| 13  | 0D  | Carriage feed     | CR   | CTRL-M    | 45  | 2D  | -     | 77  | 4D  | м    | 109 | 6D  | m    |

| 14  | 0E  | Shift out         | SO   | CTRL-N    | 46  | 2E  |       | 78  | 4E  | N    | 110 | 6E  | n    |

| 15  | OF  | Shift in          | SI   | CTRL-O    | 47  | 2F  | 1     | 79  | 4F  | 0    | 111 | 6F  | 0    |

| 16  | 10  | Data line escape  | DLE  | CTRL-P    | 48  | 30  | 0     | 80  | 50  | P    | 112 | 70  | p    |

| 17  | 11  | Device control 1  | DC1  | CTRL-Q    | 49  | 31  | 1     | 81  | 51  | Q    | 113 | 71  | q    |

| 18  | 12  | Device control 2  | DC2  | CTRL-R    | 50  | 32  | 2     | 82  | 52  | R    | 114 | 72  | r    |

| 19  | 13  | Device control 3  | DC3  | CTRL-S    | 51  | 33  | 3     | 83  | 53  | S    | 115 | 73  | s    |

| 20  | 14  | Device control 4  | DC4  | CTRL-T    | 52  | 34  | 4     | 84  | 54  | т    | 116 | 74  | t    |

| 21  | 15  | Neg acknowledge   | NAK  | CTRL-U    | 53  | 35  | 5     | 85  | 55  | U    | 117 | 75  | u    |

| 22  | 16  | Synchronous idle  | SYN  | CTRL-V    | 54  | 36  | 6     | 86  | 56  | v    | 118 | 76  | ٧    |

| 23  | 17  | End of xmit block | ETB  | CTRL-W    | 55  | 37  | 7     | 87  | 57  | w    | 119 | 77  | w    |

| 24  | 18  | Cancel            | CAN  | CTRL-X    | 56  | 38  | 8     | 88  | 58  | x    | 120 | 78  | x    |

| 25  | 19  | End of medium     | EM   | CTRL-Y    | 57  | 39  | 9     | 89  | 59  | Y    | 121 | 79  | У    |

| 26  | 1A  | Substitute        | SUB  | CTRL-Z    | 58  | 3A  | :     | 90  | 5A  | Z    | 122 | 7A  | z    |

| 27  | 18  | Escape            | ESC  | CTRL-[    | 59  | 38  | ;     | 91  | 58  | 1    | 123 | 7B  | {    |

| 28  | 1C  | File separator    | FS   | CTRL-\    | 60  | 3C  | <     | 92  | 5C  | 1    | 124 | 7C  | 1    |

| 29  | 1D  | Group separator   | GS   | CTRL-]    | 61  | 3D  | -     | 93  | 5D  | i    | 125 | 7D  | }    |

| 30  | 1E  | Record separator  | RS   | CTRL-^    | 62  | ЗE  | >     | 94  | 5E  | ~    | 126 | 7E  | ~    |

| 31  | 1F  | Unit separator    | US   | CTRL      | 63  | 3F  | ?     | 95  | SF  |      | 127 | 7F  | DEL  |

51

## The Von Neumann Model

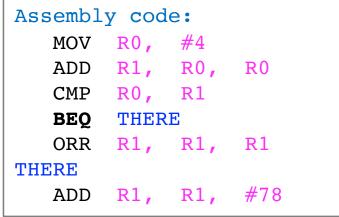

# **Control Unit**

- The control unit is like the conductor of an orchestra

- It conducts the step-by-step process of executing (every instruction in) a program

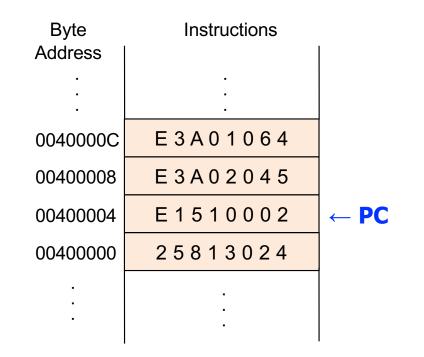

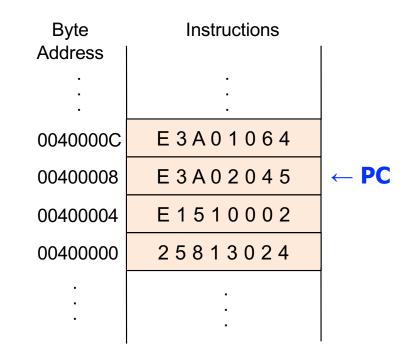

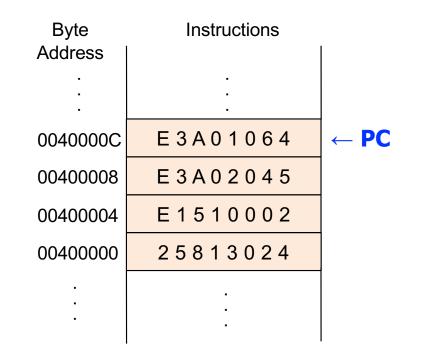

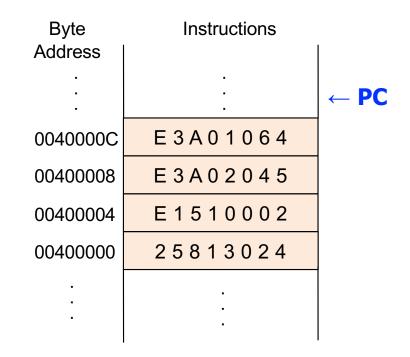

- It keeps track of which instruction being processed, via

- Instruction Register (IR), which contains the instruction

- It also keeps track of which instruction to process next, via

- Program Counter (PC) or Instruction Pointer (IP), another register that contains the address of the (next) instruction to process

PC or IP

**Inst Register**

## **Programmer Visible (Architectural) State**

| M[0]   |  |

|--------|--|

| M[1]   |  |

| M[2]   |  |

| M[3]   |  |

| M[4]   |  |

|        |  |

|        |  |

|        |  |

|        |  |

| M[N-1] |  |

#### Memory

array of storage locations indexed by an address

#### Registers

- given special names in the ISA (as opposed to addresses)

- general vs. special purpose

#### **Program Counter**

memory address of the current (or next) instruction

#### Instructions (and programs) specify how to transform the values of programmer visible state

## The Von Neumann Model

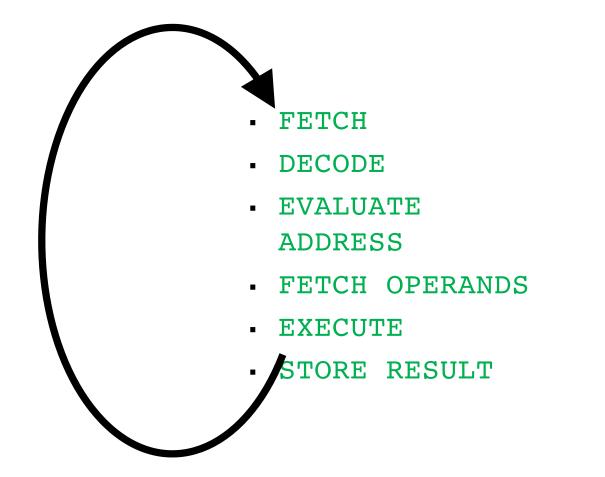

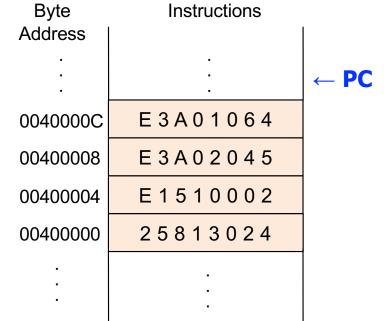

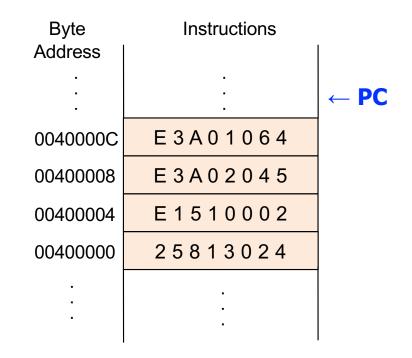

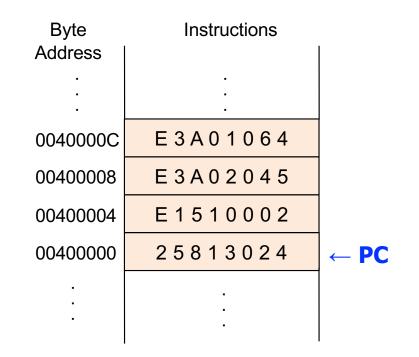

## Von Neumann Model: Two Key Properties

- Von Neumann model is also called *stored program computer* (*instructions in memory*). It has two key properties:

- Stored program

- Instructions stored in a linear memory array

- Memory is unified between instructions and data

- The interpretation of a stored value depends on the control signals

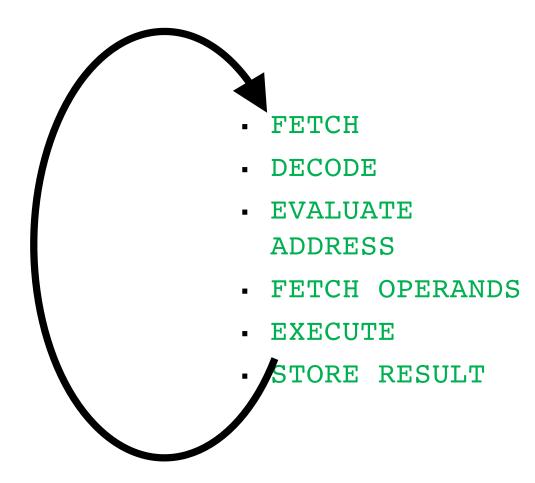

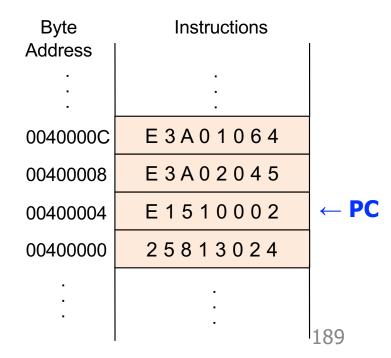

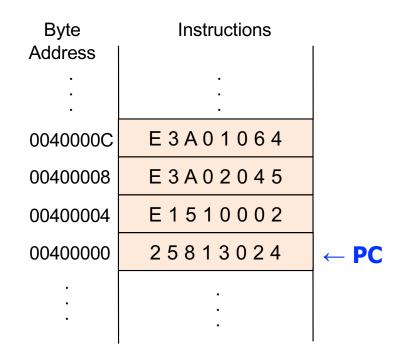

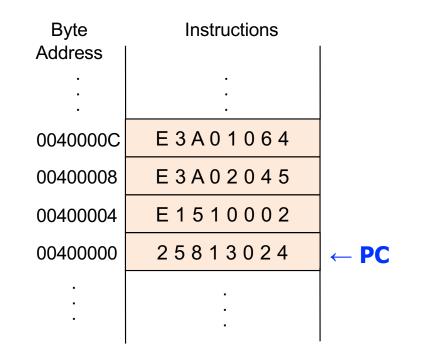

- Sequential instruction processing

- One instruction processed (fetched, executed, completed) at a time

- Program counter (instruction pointer) identifies the current instruction

- Program counter is advanced sequentially except for control transfer instructions

## The Von Neumann Model

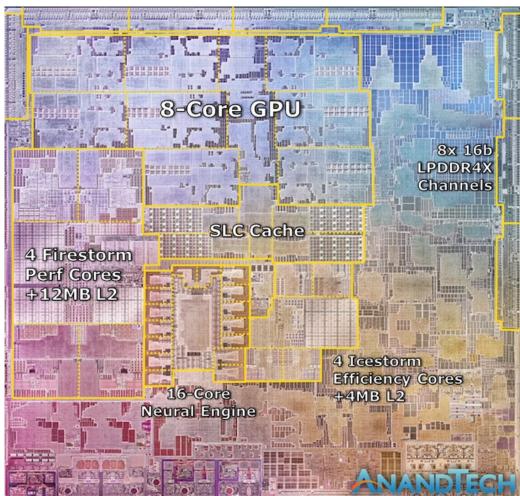

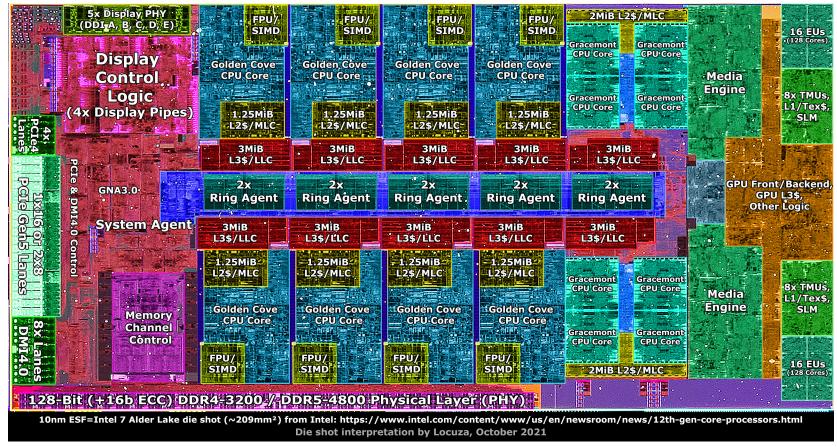

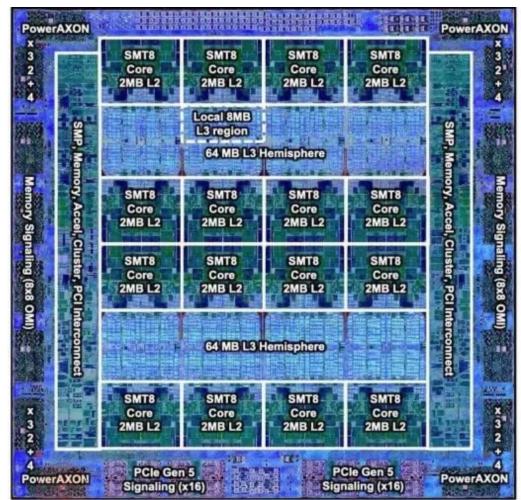

# Examples of von Neumann Machines

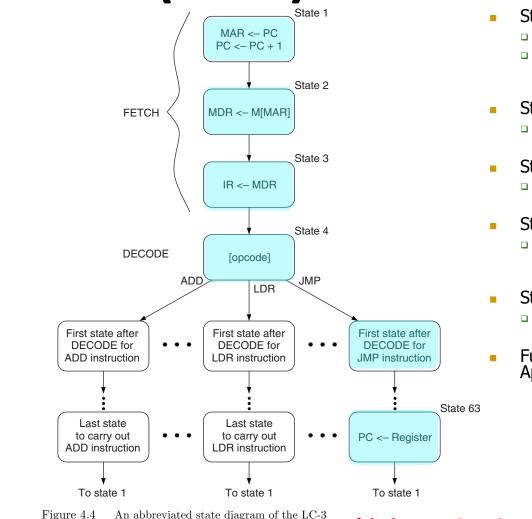

## LC-3: A von Neumann Machine

## LC-3: A von Neumann Machine

Apple M1, 2021

Source: https://www.anandtech.com/show/16252/mac-mini-apple-m1-tested

Intel Alder Lake, 2021

Source: https://twitter.com/Locuza /status/1454152714930331652

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | sa na na na na na<br>sa na na na na | en de la servicient<br>Rei de la servicient<br>Rei 1991 - Hartorius | N. C. State (1997) And C. | and the last has a multiple<br>and the last has a multiple<br>and the Distance |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Debug, Wafer tests bumps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | an and an an and                    | Global Memory I<br>(Infinity                                        | nterconnect 2.<br>Fabric)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | an las in 1993<br>An las in 1998<br>An las 1997 (1993)                         | System Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

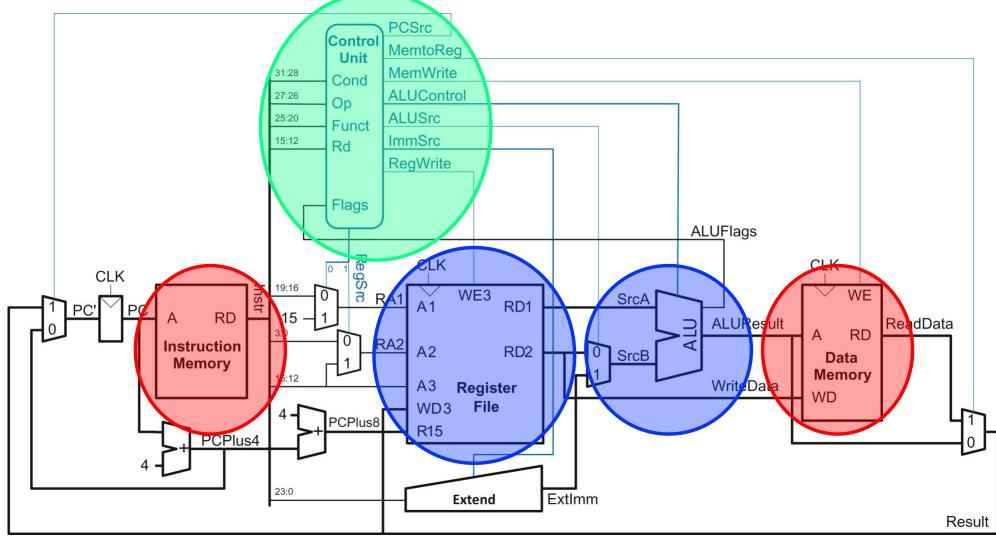

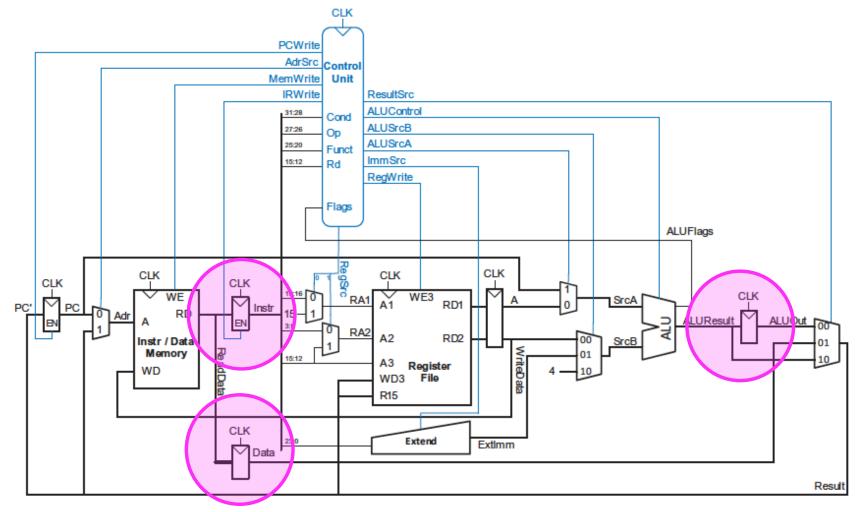

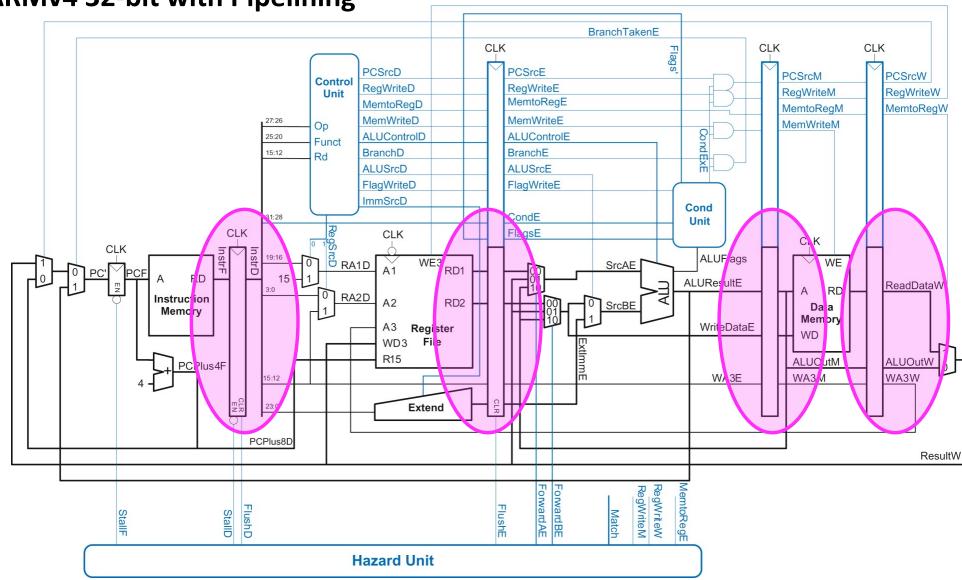

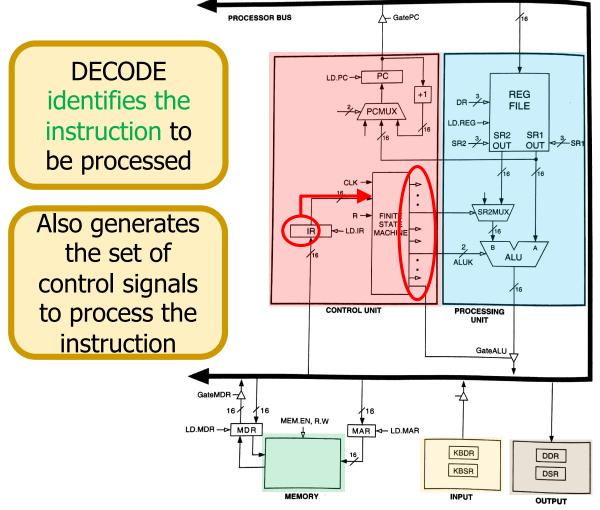

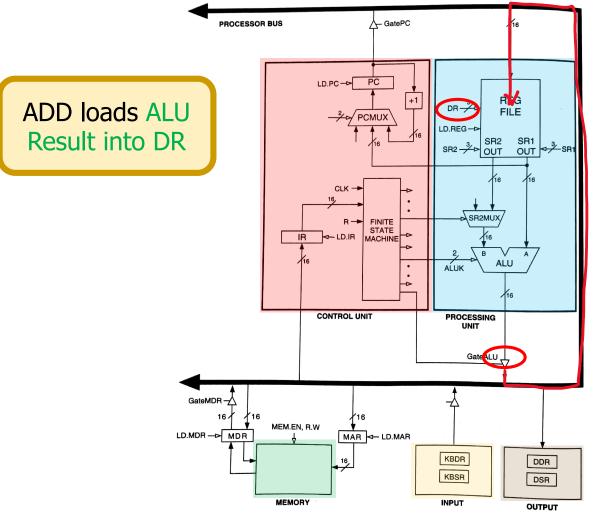

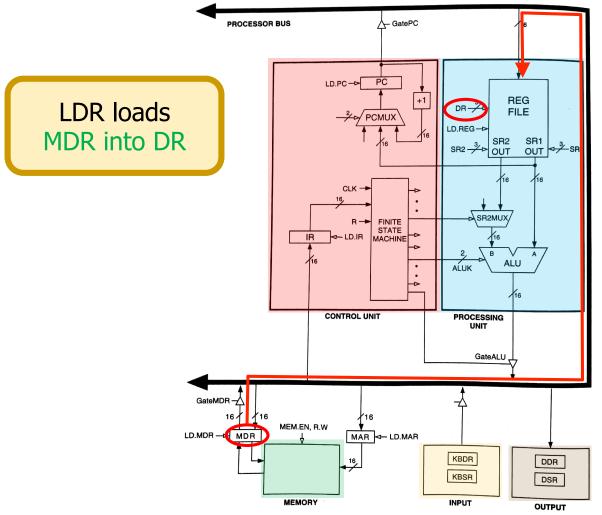

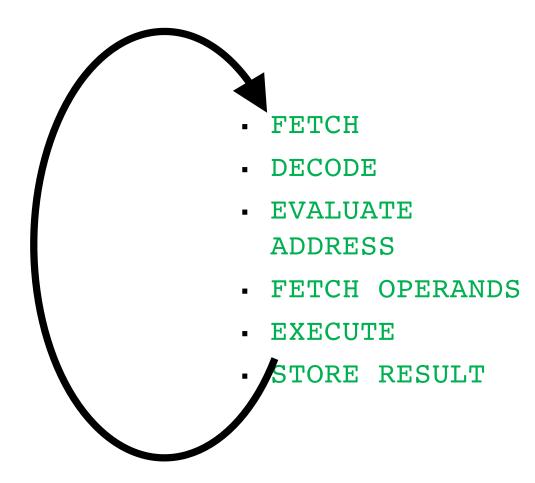

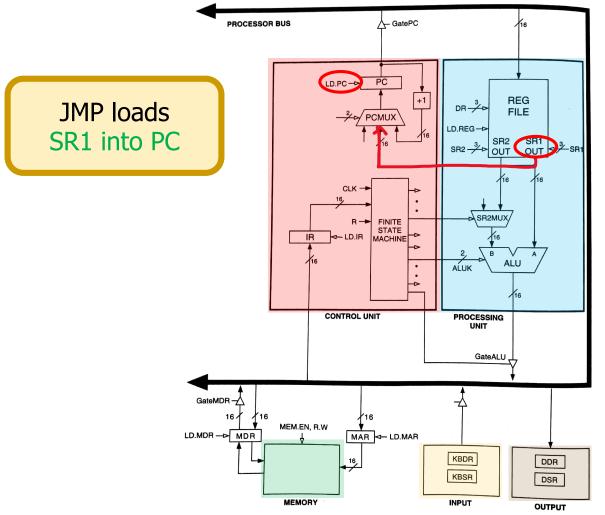

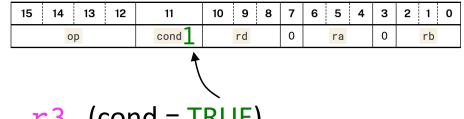

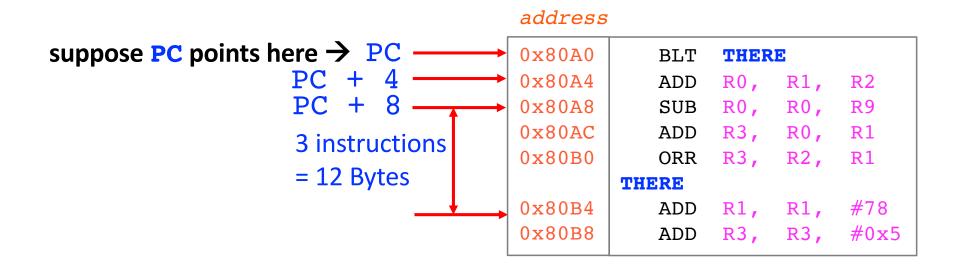

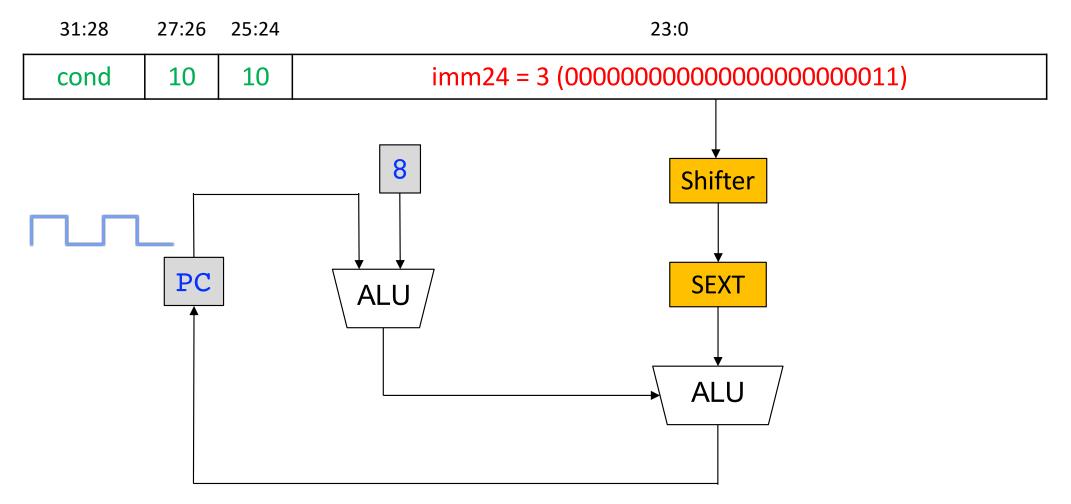

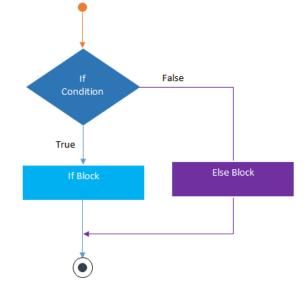

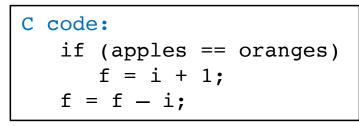

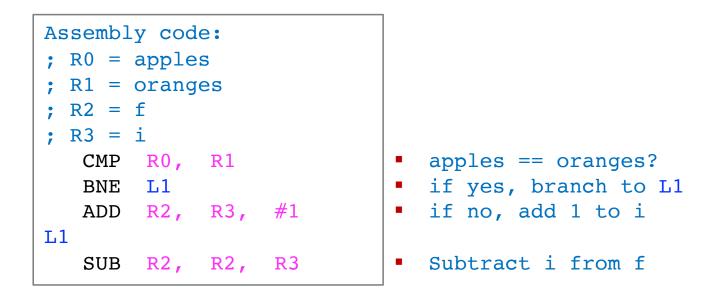

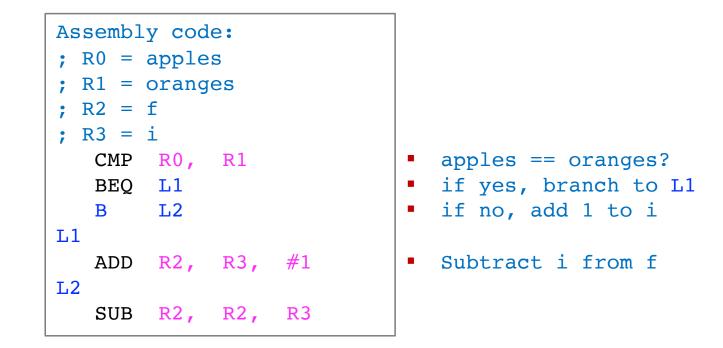

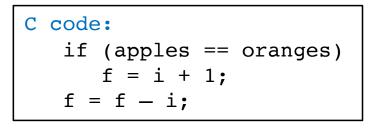

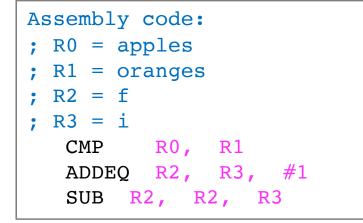

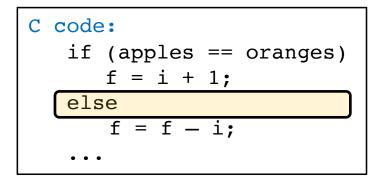

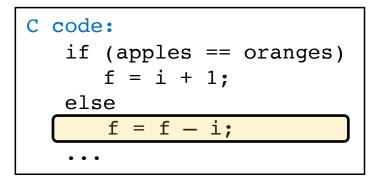

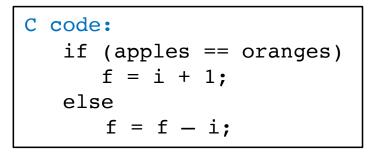

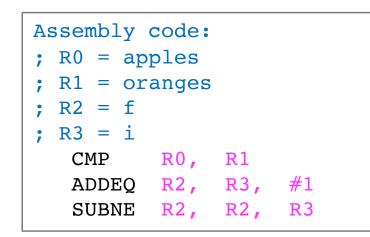

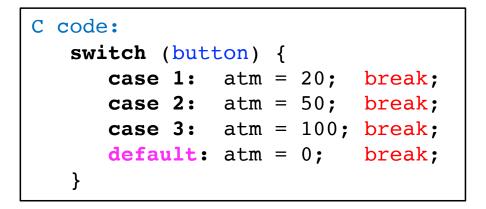

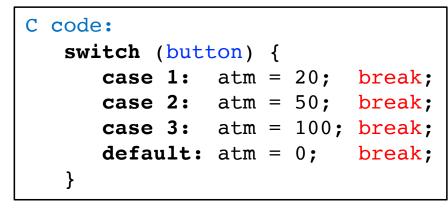

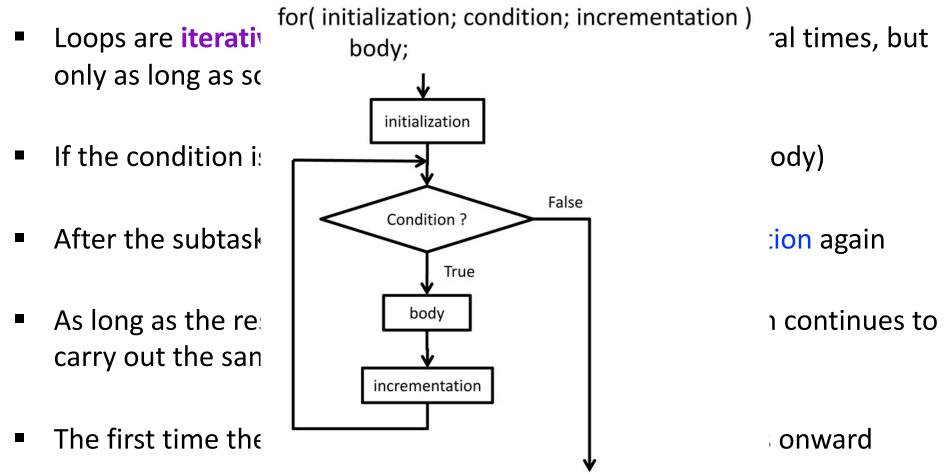

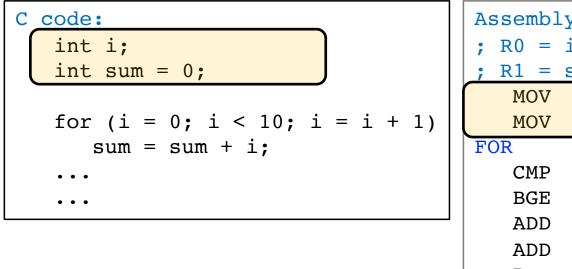

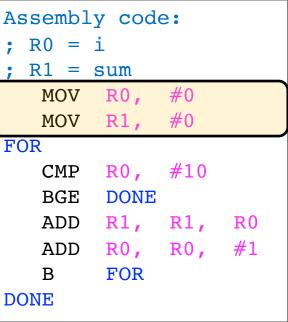

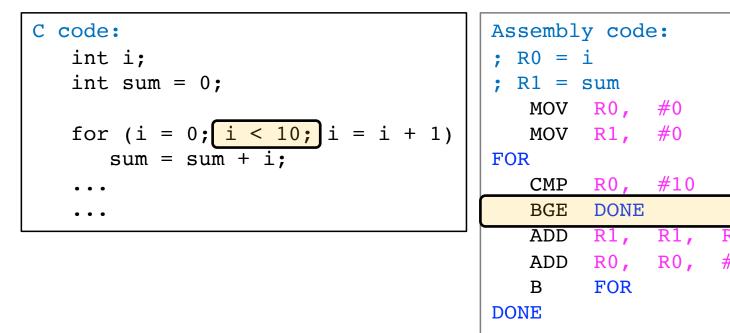

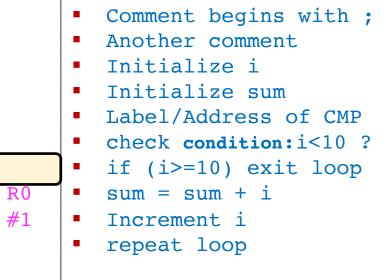

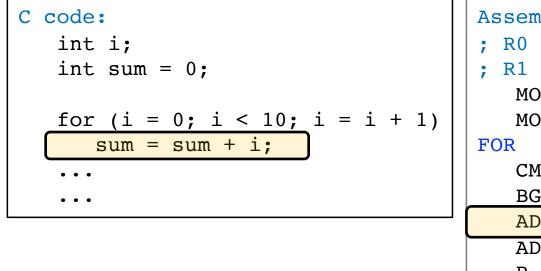

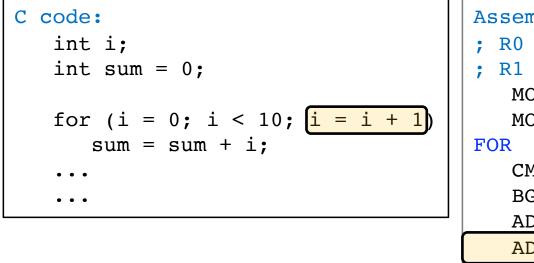

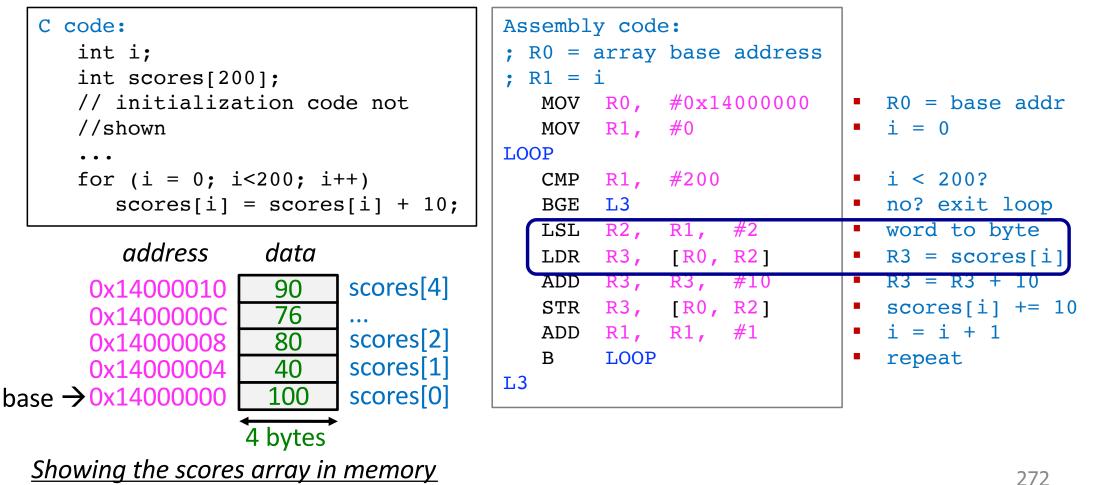

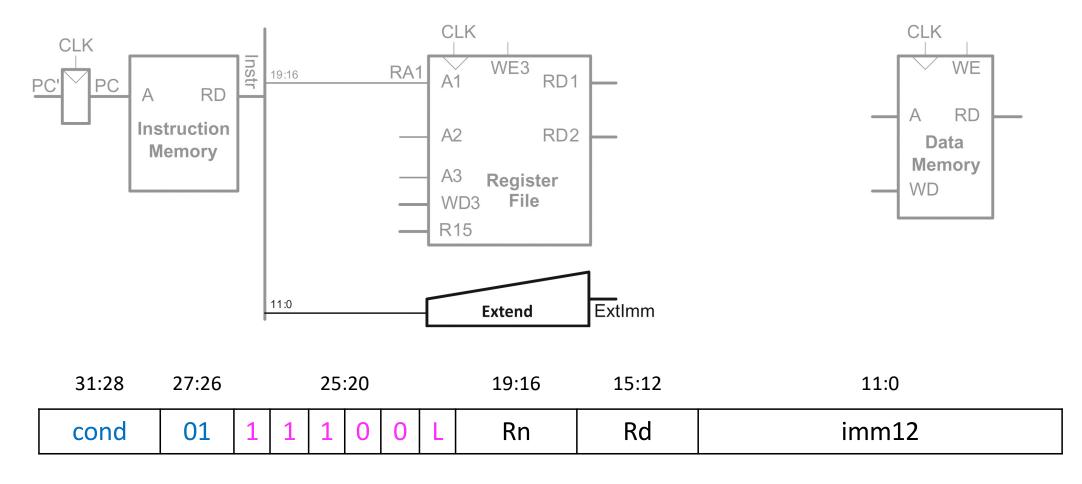

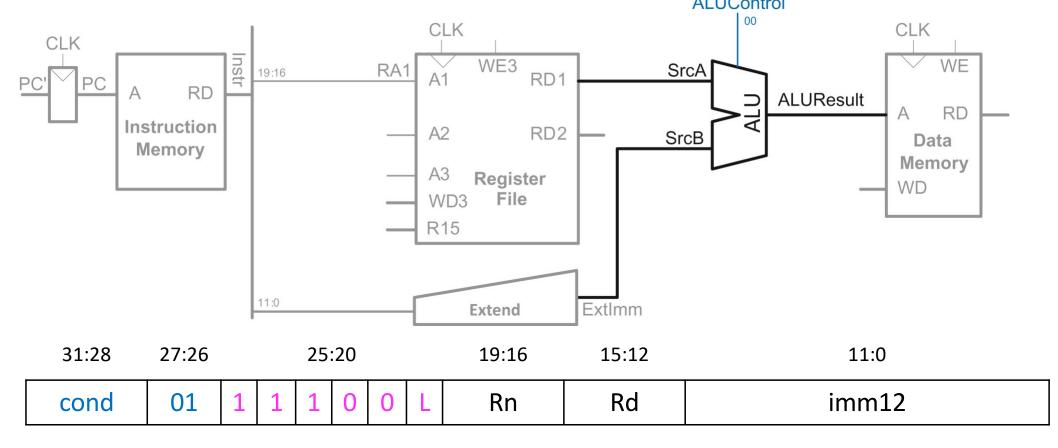

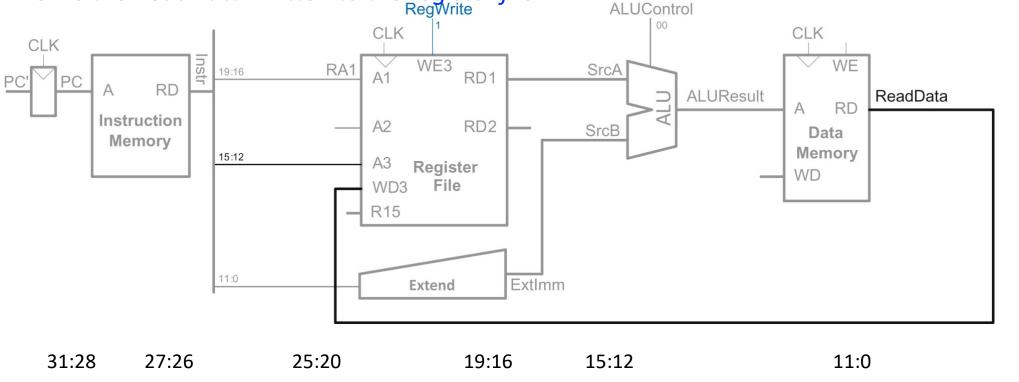

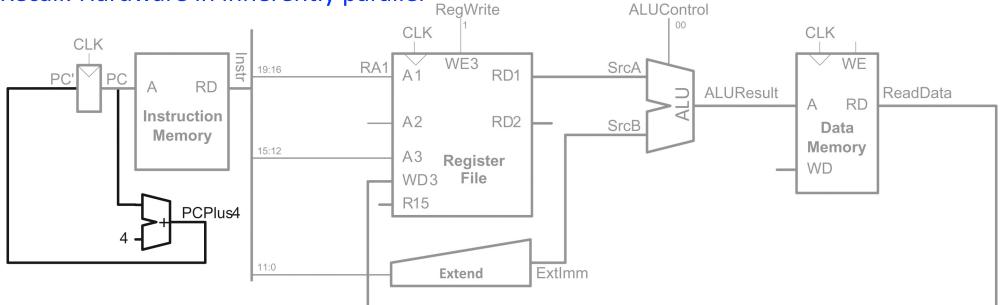

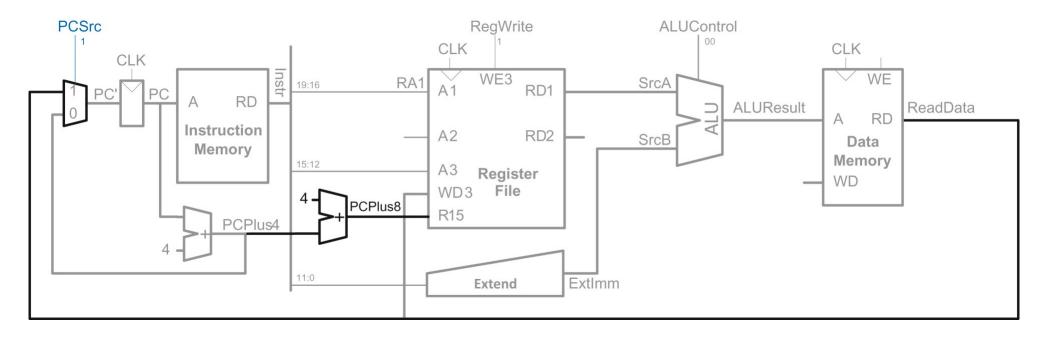

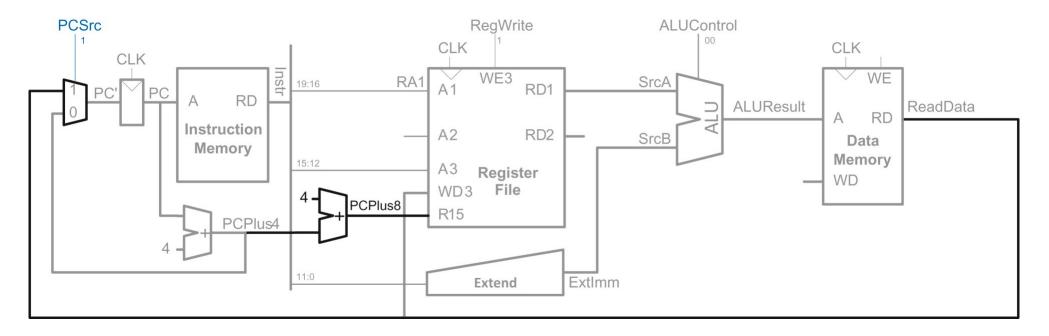

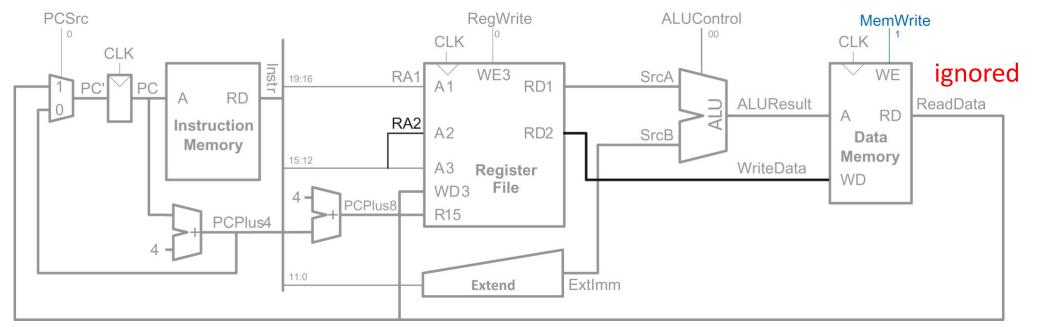

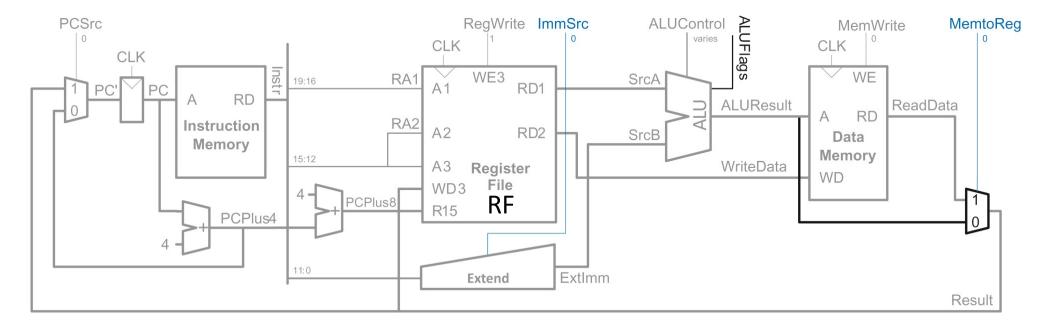

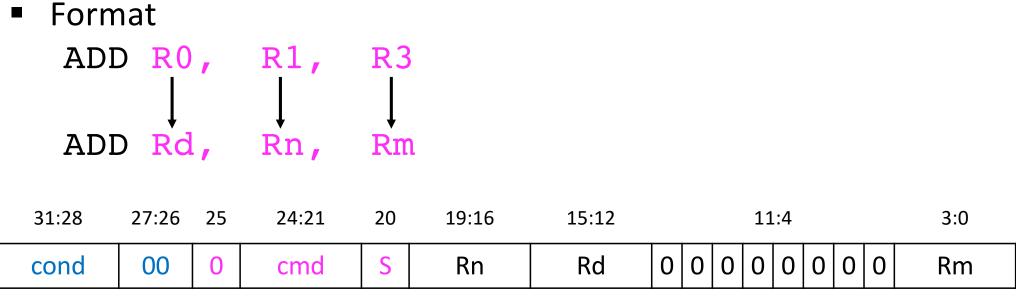

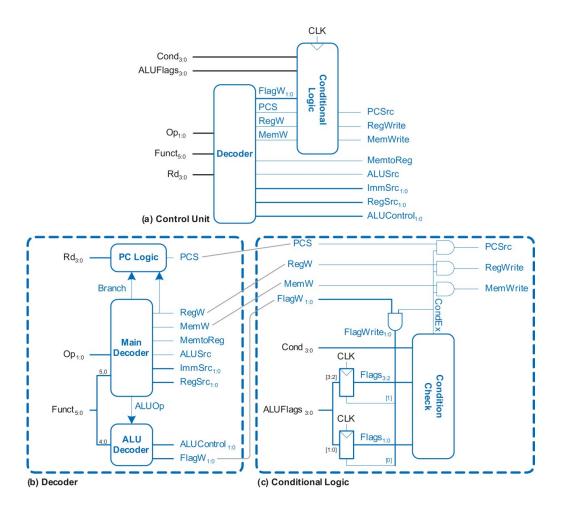

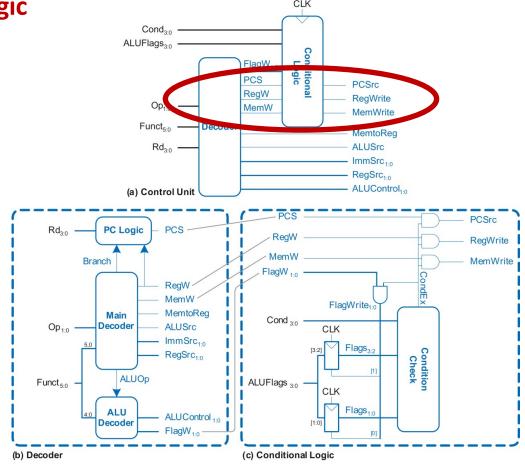

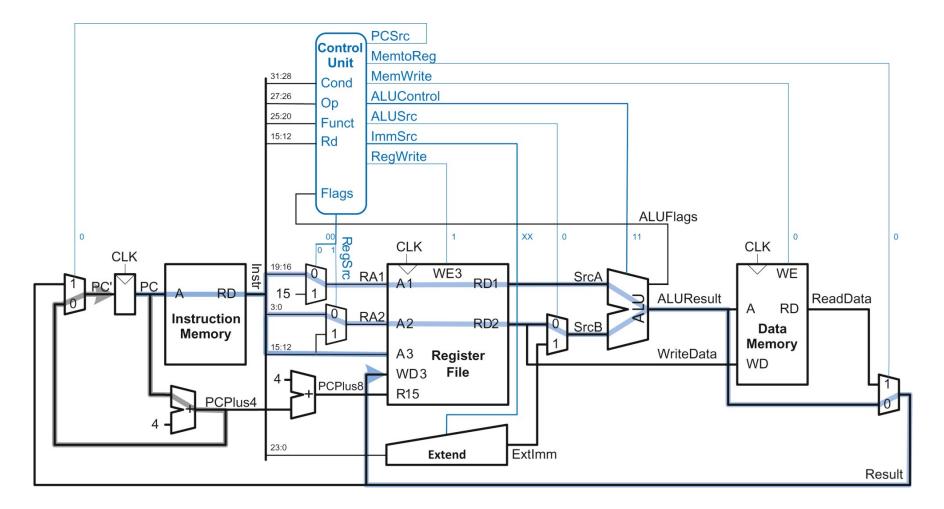

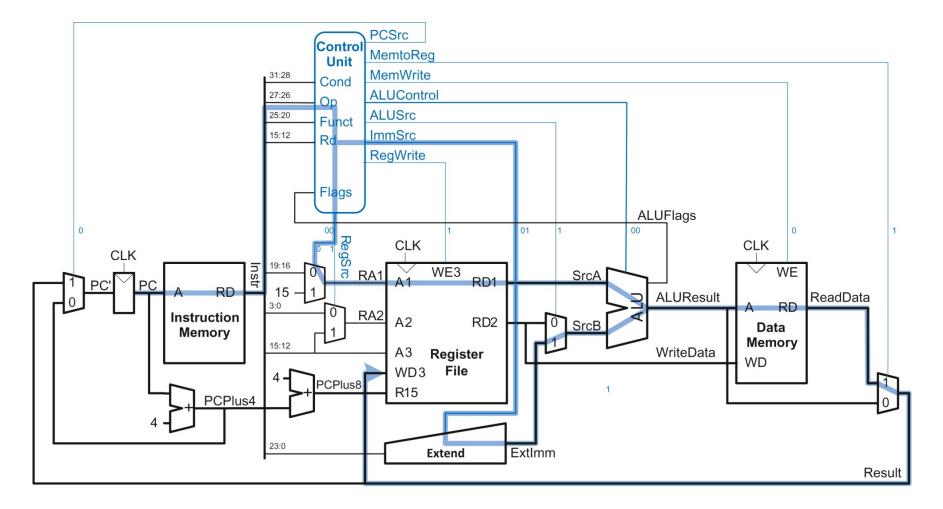

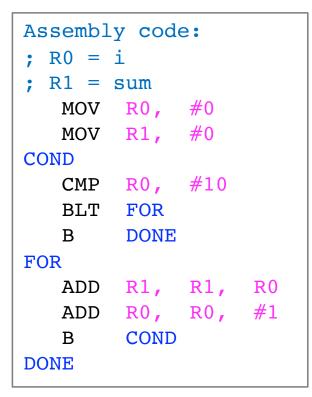

| courrou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1 Mill L35 Array                    | L Mill L35 Array                                                    | 1 HIB L35'Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 MiB L3\$ Array                                                               | L2 Cache 1 Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |